顯示控制器S680724的接口技術

摘 要:設計點陣液晶屏顯示控制器S680724與嵌入式處理器SEP3203的接口電路,解決3V電壓總線與5 V電壓器件的雙向傳輸問題。介紹使用一個片選信號控制多個顯示控制器的設計技巧,同時給出其初始化程序。

關鍵詞:SEP3203 S680724 顯示控制器 接口技術

引 言

S680724是Samsung公司1999年推出的一款大規模的顯示控制驅動芯片,用于控制和驅動點陣式液晶屏。這款顯示控制芯片將控制電路、RAM和驅動電路集成在單一芯片中,使其在系統成本方面具有優勢。SEP32O3是由東南大學國家ASIC工程中心設計的一款基于ARM7TDMI內核的16/32位嵌入式微處理器。雖然SEP3203自帶LCD控制器,但是其信號適用于不帶RAM的灰度或彩色液晶屏,不支持在工控系統中常使用的帶RAM的黑白液晶顯示屏,所以工控系統應用中需要通過外接顯示控制器來實現液晶顯示。下面介紹S680724顯示控制器在以SEP3203為核心的工控系統中的應用。

1 系統介紹

1.1設計要求

系統要求通過總線掛接的方式實現64192黑白點陣的顯示。該點陣屏的規格較特殊,但在電話終端和小型收款機等工控系統中經常使用。常見的幾款中小規模顯示由DSP自身的硬件來協調沖突,因此HPI-8口適用于與單片機構建較好的主從雙CPU處理器平臺。控制器[2.3]所控制的點陣范圍都比其小(65132,132176)。需要用2片S680724控制該液晶屏,同時要求只使用1個片選信號來實現對2片S680724的控制。

1.2系統構成

系統主要由SEP3203處理器、電平轉換芯片74LVXC4245和74HCT541,以及2片S680724顯示控制器組成,如圖1所示。SEP3203是一款16/32位嵌入式微處理器,由東南大學國家ASIC工程中心設計。采用業界標準的ARM7TDMI內核,AMBA總線結構。SEP3203處理器內嵌20 KB零等待的靜態存儲器(SRAM),提供SDRAM控制器;可支持NOR Flash、NAND Flash啟動;可擴展支持各種SRAM接口的設備;提供可自由控制的GPIO口,同時具有多種控制器接口。

S680724是一款顯示控制驅動芯片,最大支持65132的點陣顯示,同時提供主從式結構的擴展;內部帶有RAM,可以支持屏幕自刷新;有65個common輸出,165個segment輸出。它的MPU接口可支持8080和6800兩種時序模式。模式的選擇通過配置外部引腳來實現。

由于單片S680724只支持65132點陣的顯示,而設計要求實現64192點陣的顯示,因此在圖1中使用了2片S680724。另外,由于S680724使用5 V信號,Vm的最小值為4 V(0.8VDD),而SEP3203的總線采用的是3 V信號(通常的嵌入式CPU使用的都是3 V總線),所以SEP3203無法直接驅動S680724,需要作電平轉換。因此圖1中在SEP3203與S680724之間增加了電平轉換芯片,以實現3 V信號與5 V信號的雙向轉換。

電平轉換芯片選用的是74LVXC4245 和74HCT541。這兩款芯片都是普通的邏輯芯片,很多公司都生產。74LVXC4245是雙向電平轉換芯片,3 V和5 V兩路電源供電;可以支持3 V到5 V的雙向電平轉換,但需要有信號控制電平轉換方向。74HCT541是單向的緩沖芯片,采用5 V電源,可以將輸入的3 V信號轉換成5 V信號后輸出。

2 硬件設計

2.1 總線接口的分析

S680724可與各種MPU相連,具體連接方式取決于MPU所使用的總線類型。其提供兩種MPU的信號接口協議:一種是6800系列MPU接口協議,如圖2所示;另一種是8080系列MPU接口協議.如圖3所示。將兩種接口協議與SEP3203的接口協議對比,可見SEP3203的接口協議屬于8080接口協議,因此采用8080的接口實現S680724與SEP3203的連接。SEP3203的接口協議如圖4所示。

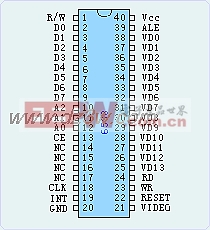

根據8080接口協議,S680724與MPU接口信號的定義如表1所列。

S680724的DO~D7信號應與SEP3203的DATAO~DATA7信號連接;S680724的RD、WR、CS信號應分別與SEP3203的OE、WE、CS信號連接。RS是訪問控制寄存器與RAM的選擇信號――RS為低時訪問S680724的控制寄存器.RS為高時訪問S680724中的RAM。其作用相當于地址信號,因此與SEP3203的地址線連接。RST是S680724的復位信號,可由SEP3203的GPIO產生。

2.2雙8680724控制器接口設計

由于要支持64192的點陣顯示,所以在該設計中需要使用2片S680724(以S680724一A和S680724_B來表示)。圖1中S680724_A控制液晶屏的64132個點,S680724_B控制剩下的64X 60個點。由于總線設備較多,只有1個片選信號能用于對2片S680724芯片的操作;同時56130724與SEP3203的總線也需要作電平轉換,因此在該接口設計中利用了電平轉換芯片實現了該功能,并沒有再增加額外的邏輯芯片。分析S680724與MPU的接口信號,發現其中RD、WR、RST、CS、RS信號只需單向傳輸(從MFU傳向S680724),只有DO~D7信號需要雙向傳輸。圖5中,使用74HCT541實現3 V信號到5 V信號的單向電平轉換,74LVXC4245實現3 V信號與5 V信號的雙向電平轉換。

圖3中CSlB、CS2、RS信號是同時變化的(CSlB信號為低,CS2信號為高時S680724被選中)。由于在實際使用中CS2信號是固定接高電平,所以CSlB信號就是文中S680724芯片的CS信號。圖4中SEP3203總線的地址信號和片選信號也是同時變化的,因此考慮使用地址信號來代替片選信號。但如果直接用地址信號來代替片選信號會導致總線對其他設備操作時也選中S680724,即兩個總線設備被同時選中,從而產生錯誤。在該設計中,利用電平轉換芯片的特性解決了這一問題。如圖5所示,使用了ADDR3、ADDR4作為S680724的片選信號(LCD_CSA、LCD_CSB)。ADDR2作為選擇對S680724寄存器或RAM操作的信號(LCD)_RS)。SEP3203的片選信號ICDnCSF連接74HCT541的使能端()E。當LCD_nCSF信號為低時74HCT54l被使能,OE、WE、ADDR3、ADDR4、ADDR2信號被轉換成相應的5V信號(LCD/RD、LCD_/WR、LCD_CSA、LCD_CSB、LCD_RS)輸出到S680724;當LCD_nCSF信號為高時74HCT541停止工作,此時74HCT54l輸出高阻態,為避免噪聲干擾,輸出端信號LCD_/RD、LCD_/WR、LCD_CSA、LCD_CSB、LCD_RS應被上拉至5 V。在SEP3203的片選LCD_nCSF無效(高電平)時,由于信號LCD_CSA、LCD_CSB被拉高,所以此時2片S680724控制器都未被選中,任何操作對其都是無效的,從而避免了在總線對其他設備操作時可能對S680724產生的誤操作。

數據信號的電平轉換類似于控制信號的電平轉換。74LVXC4245是雙向電平轉換芯片,圖5中的LCD_DIR信號由SEP3203的GPIO產生,用于控制74LVXC4245電平轉換方向的信號。當LCD_DIR為低時,信號由B端傳向A端,即由總線傳向S680724(寫操作);當LCD_DIR為高時,信號由A端傳向B端,即由S680724傳向總線(讀操作)。信號LCD_DO~LCD_D7也需要上拉,防止當74LVXC4245的輸出為高阻時,外部噪聲在其輸出端產生錯誤信號。

值得一提的是,S680724顯示控制器在PCB板上的位置靠近液晶屏,與SEP3203之間的距離很大。在PCB布局時,需要注意電平轉換芯片的位置。因為其不但有電平轉換的作用,而且還能緩沖總線信號,使總線和S680724顯示控制器隔離,避免總線過長。電平轉換芯片的布置應該盡量靠近總線,減小總線的長度,從而避免產生由總線過長造成的信號延時及噪聲干擾問題。

雖然RST信號也是單向傳輸的,但RST信號的電平轉換電路卻是單獨設計的。如果使用74HCT541完成電平轉換,會有兩個問題:①當LCD_nCSF失效時74HCT541不工作,此時LCD__RESET信號無法傳遞到RST端,RST端始終是高電平(被上拉至5 V),因此S689724無法被復位;②在74HCT541工作時,因為LCD_nCSF的脈沖寬度等于總線周期(最大值約為幾百ms).所以輸出的RST信號的最大脈沖寬度也等于總線周期;而S680724要求的RST信號最小脈沖寬度是1μs,所以用74HCT541無法產生正確的RST信號,此時S68072同樣無法被復位。在圖5中,該信號的電平轉換電路是由晶體管和電阻構成的。

3 驅動程序

該部分軟件主要是依照S680724的初始化流程、命令參數列表及其他資料編寫的。S680724的訪問地址只有兩個:一個是寄存器地址(通過寫入不同的命令字來實現對S680724的控制);另一個是RAM端口(顯示數據由此寫入)。

首先需要根據S6B0724的接口設計計算其各端口的訪問地址。SEP3203的片選信號LCD_nCSF所對應的基址是0x34000000。圖5中S680724_A、S680724_B的寄存器訪問地址分別是0x340000100、0x34000020;RAM的訪問地址分別是0x34000018、0x34000028。特別是在該接口設計允許SEP3203同時訪問S680724_A和S680724_B,寄存器的訪問地址為0x34000000,RAM的訪問地址為0x34000008。在實際使用中。可以利用這個特點對兩個控制同時初始化,提高軟件效率。

S680724的初始化流程如圖6所示。先冷復位S680724,然后將74LVXC4245的電平轉換方向設置為從總線向數據線。通過寫S680724的控制寄存器對S680724軟復位,然后選擇所用的顯示方式和掃描方向,再選擇背光亮度;通過寫寄存器的方式打開S680724內部的電壓反轉器,等待10 ms后再打開電壓生成器。延遲10 ms后,打開電壓跟隨器,等所有電壓都穩定后(約等待10 ms)再設定液晶屏的工作電壓,最后開始顯示。圖像的顯示通過函數void Write_alILCD(void)來實現。其功能是將所要顯示的點陣數據送入2片S680724。

初始化程序如下:

void GPC)_init(void){

RESET_LCD();

//冷復位

*(RP)PORTB_SEL l=(18);

//設定74LVXC4245的電平轉換方向

*(RP)PORTB_DATA 8L=~(18);

*(RP)PORTB_DIR&=~(18);

*(RPl6)ADDR_LCD_CMD=INTER_RESET;

//2片S6B0724B同時軟復位

1NIT_LCD(); //初始化S680724B

*(RPl6)ADDR_LCD_CMD=DISPLAY_ON;

//初始化完畢開始顯示

Clear_LCD(); //清屏

}

4結論

該設計已在以SEP3203為核心的嵌入式系統中被實際應用。采用S680724顯示控制器后,解決了SEP3203微處理器在工控應用中使用液晶屏的問題。使用1個片選信號實現了對2個顯示控制器的控制。2個以上顯示控制器的控制也可通過類似方法實現。該設計可以在金融收費系統、稅務管理系統、電話終端等眾多系統中應用。

評論