基于FT245BM和FPGA的USB接口設計

摘要介紹了USB協議芯片FT245BM的工作原理,設計了FT245BM與FPGA的接口電路,給出了FPGA發送和接收數據幀狀態機的Verilog語言的描述,并介紹了PC機軟件的設計方法。該電路被成功地應用到光纖陀螺多路測試系統中,簡化了電路設計,提高了測試效率。該設計具有很強的通用性。

關鍵字通用串行總線(USB)FT245BMFPGA狀態機

一、引言

USB總線因其傳輸速度快、占用資源少以及真正的即插即用等諸多優點,受到了廣大開發者的青睞,已經成為很多計算機設備的一種基本配置。目前被廣泛采用的USB設備開發方案主要有以下兩種(1)利用USB設備端接口芯片加微控制器結構。如國內用的比較多的Philips公司的PDIUSBD12/ISP1581等。(2)采用USB單片機。采用這兩種方案要求開發者徹底理解USB協議的細節,并編寫出固件程序。固件的運行要占用微控制器的時間和空間資源,實際通信效率不會很高。也有人用FPGA實現固件的功能,但這種方案開發和調試的難度很大。本人在實際工作中用FPGA外部直接連接一片USB協議芯片FT245BM,實現了FPGA與PC機的USB通信,該方法不用微控制器,減少了元器件的個數,并且占用FPGA資源很少,FPGA仍然可以實現其他邏輯功能,系統設計的靈活性很大。

二、FT245BM簡介

FT245BM由FTDI (Future Technology Devices Int. Ltd.)公司推出,該芯片的主要功能是進行USB和并行I/O口之間的協議轉換。芯片一方面可從主機通過USB串行總線接收數據,并將其轉換為并行I/O口的數據流格式發送給外設;另一方面外設可通過并行I/O口將數據轉換為USB串行數據格式傳回主機。中間的轉換工作全部由芯片自動完成,開發者無須考慮固件的設計。該芯片提供了通用的并行I/O口方便與微控制器、FPGA或其他外設接口。在PC機端安裝了FTDI公司提供的驅動程序,只需熟悉簡單的VB、VC編程,就可很容易地進行上位機軟件開發。

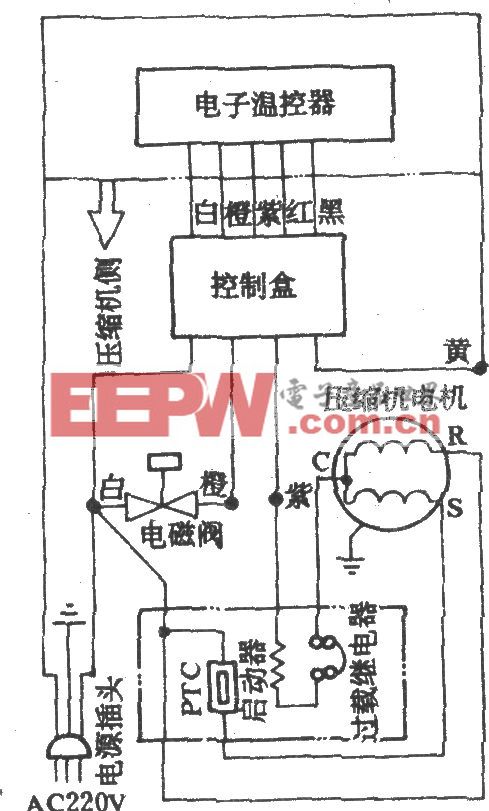

關于FT245BM的內部結構及詳細地引腳介紹讀者可以參考其他相關資料,在此僅對與本設計相關的內容作一個介紹。FT245BM內含兩個FIFO數據緩沖區,一個是128字節的接收緩沖區,另一個是384字節的發送緩沖區。它們用作USB數據與并行I/O口數據的交換緩沖區。FIFO實現與外界(微控制器、FPGA或其它器件)的接口,主要通過8根數據線D0~D7、讀寫控制線RD#和WR#以及FIFO發送緩沖區空標志TXE#和FIFO接收緩沖區非空標志RXF#來完成數據交互。TXE#為低表示當前FIFO發送緩沖區為空,為高表示當前FIFO發送緩沖區滿或者正在存儲前一個字節,禁止向緩沖區中寫數據。RXF#為低表示當前FIFO的接收緩沖區非空。RD#信號由低變高將從FIFO緩沖區中讀取數據。當RD#變低時將數據送到數據總線。RXF#為高不能從FIFO讀數據。讀寫時序見圖1和圖2。

圖2 寫數據時序

三、 FT245BM與FPGA的接口設計

3.1 硬件電路設計

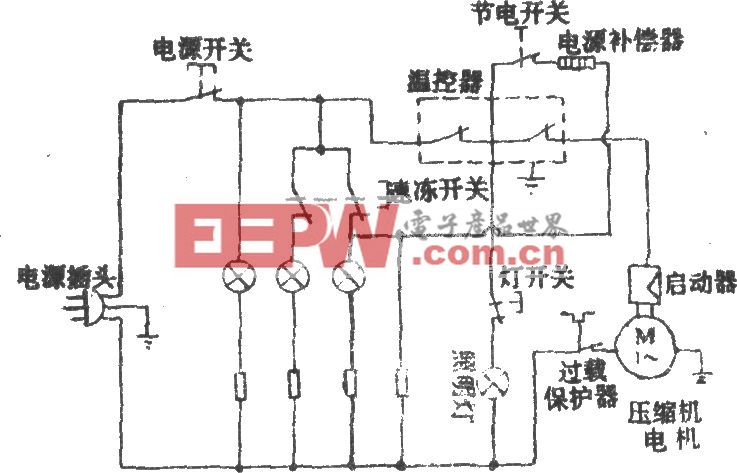

圖3是FT245BM的USB與FPGA的接口電路,FPGA選用ALTERA EPF1K50TC-144,其中D0~D7是FT245BM與FPGA交換數據的數據總線,USB_RD#、USB_WR、USB_TXE#、USB_RXF#是相關的控制總線。

圖3 FT245BM與FPGA的接口電路

3.2 FPGA收發狀態機設計

下面是用Verilog HDL 描述的FPGA收發狀態機,為便于讀者理解FPGA對FT245BM的讀寫過程,本文將接收和發送狀態機分開給出。當然在實際應用中也可以將接收和發送操作合成一個狀態機來實現。

3.2.1 接收狀態機

接收狀態機主要功能是查詢USB_RXF引腳的狀態,當檢測到USB_RXF變低,即可獲知上位機已經將數據寫入到FT245BM的緩沖區,然后產生讀控制時序,將FT245BM接收緩沖區中的數據讀入到FPGA的緩沖區。重復以上步驟直到將一幀數據讀完,然后執行相應的幀處理操作。下面是用Verilog HDL描述的接收狀態機。

@always (posedge clk ) /*clk為FPGA工作時鐘。

if(rst USB_RXF==0)

begin

case(Rstate)

Rstate0:

begin

USB_RD=0; /*產生讀信號的下降沿

Rstate=Rstate1;

end

Rstate1:

begin

RframeBuf[Rpointer]=USB_DATA; /*讀FT245BM芯片FIFO的當前字節

Rstate=Rstate2;

end

Rstate2:

begin

if(Rpointer== FrameLen-1) /*如果已經接收到完整的一幀,則轉Rstate3,

begin

Rstate=Rstate3;

Rpointer=0;

end

else /*一幀未接收完,轉Rstate0繼續接收

begin

Rstate=Rstate0;

Rpointer=Rpointer+1;

end

USB_RD=1;

end

Rstate3: /*處理收到的幀

begin

Rstate=Rstate0;

/*在此添加處理幀的代碼,本文略*/

end

end

else

begin

Rstate=Rstate0;

USB_RD=1;

End

3.2.2 發送狀態機

發送狀態機完成的主要功能是將外設產生的數據通過FT245BM和USB總線傳送到PC機。外設將數據準備好后,將發送允許信號(SendEN)置為有效,當狀態機檢測到SendEN=1時,即啟動發送操作。首先狀態機從外設的緩沖區按字節將待發送的數據讀到FPGA的緩沖區,并產生寫FT245BM發送緩沖區的時序,將數據寫到FT245BM發送緩沖區。直到將一幀數據發送完畢。下面是FPGA向FT245BM發送數據的狀態機。

@always (posedge clk ) /*clk為FPGA工作時鐘。

if(rst USB_TXE==0 SendEN==1) /*rst為異步復位信號, SendEN為發送允許信號,由給Pc機發送數據的邏輯電路置位,數據發送完成由發送狀態機將其清除。

begin

case(Sstate)

Sstate0:

begin

USB_WR=1; /*產生寫信號的上升沿

Sstate=Sstate1;

end

Sstate1:

begin

USB_DATA =SframeBuf[Spointer]; /*寫一個字節到FIFO,SframeBuf為發送緩沖區

Sstate=Sstate2;

end

Sstate2:

begin

if(Spointer == FrameLen-1) /*如果已經發送完一幀,則轉Sstate3,

begin

Sstate=Sstate3;

Spointer =0;

end

else /*未完,轉Sstate0繼續發送

begin

Sstate=Sstate0;

Spointer = Spointer +1;

end

USB_WR=0; /*產生寫usb FIFO信號的下降沿

end

Sstate3:

begin

Sstate=Sstate0;

/*在此添加處理幀發送完畢的代碼和清除SendEN 信號的代碼,本文略*/

end

end

else

begin

Sstate=Sstate0;

USB_WR=0;

End

限于篇幅,以上狀態機只給出了幀收發的基本操作,因為在不同的應用場合,幀處理的方法也不相同,所以本文沒有給出幀處理代碼。另外,在實際應用時需要注意以下內容:由于FPGA讀寫FT245BM共用一組數據總線,狀態機不能同時對FT245BM進行讀寫操作,當所以當兩個狀態機分開編寫時,為避免沖突需分出讀寫的優先級,此時只需對以上狀態機稍加修改即可。比如當若令讀的優先級高,則在寫的狀態機中將if(rst USB_TXE==0 SendEN==1)語句的條件改為if(rst USB_TXE==0 SendEN==1 USB_RXF==1)即可。寫優先級高的情況可以仿照此方法修改。

四、PC機軟件設計

PC機軟件的設計有兩種方法:一種是在PC機上安裝一個由FTDI公司免費提供的虛擬串行口VCP(Virtual COM Port)驅動程序,將USB口虛擬成一個串口,像一個標準的串口那樣進行進行外設和PC機的通信。可本質上所有針對虛擬串口的數據通信都是通過USB總線完成的。另外一種方法是利用FTDI公司提供的D2XX驅動程序,通過調用驅動程序的動態鏈接庫直接訪問USB。由于人們對串口的操作比較熟悉,通常用前一種方法訪問USB。比如,在PC端,應用VB對VCP(通常設置為COM3)進行編程。可以直接應用MSComm控件,將MSComm.CommPort置為3,MSComm.Setings置為“9600,n,8,1”(該速率為默認設置,實際上VCP驅動程序總是使數據以最快速率傳輸);通過MSComm.PortOpen設置COM3的開關狀態;通過MSComm.Input和MSComm.Output讀入或輸出數據。在讀取數據時,設置MSComm.Rthreshold的值為1。只要有數據傳到PC機,就立即觸發MSComm.CommEvent事件,自動讀取COM3的數據;而發送數據則可自動或手動發送,由用戶自己設置。以上操作與操縱標準的串行口完全一致。

五、結語

以上狀態機在MaxPlusII10.2下調試并下載到FPGA運行通過,軟件在Windows 2000,VB6.0環境下調試通過。該電路成功應用到光纖陀螺多路測試系統中,實現了同時對4路陀螺信號的同時測試,簡化了電路設計,提高了測試效率。

參考文獻:

[1] FT245BM data sheet. Future Technology Devices Int. Ltd.

[2] 夏宇聞. Verilog 數字系統教程[M]. 北京:北京航空航天大學出版社,2004

[3] 張俊安. 用VB實現windows 9x環境下的串口通信[J]. 山東煤炭科技, 2000年增刊:73~74

評論