SOPC中NiosII的LCD顯示驅動IP設計

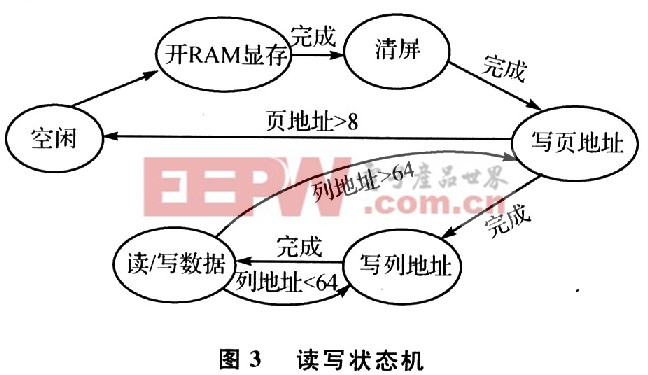

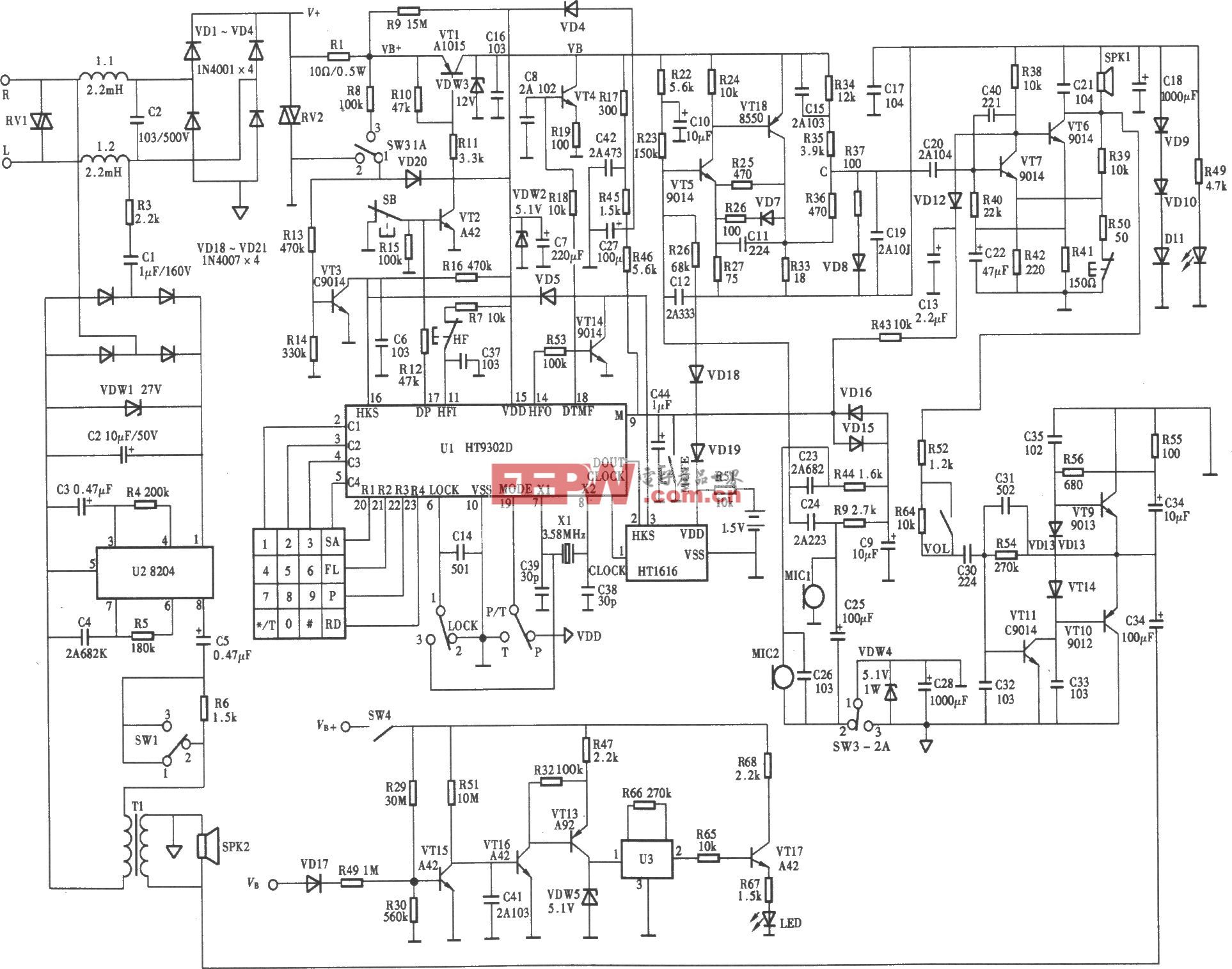

如圖3所示,讀寫狀態機給出讀或者寫信號,并在讀寫控制狀態機的控制下,完成寫命令、寫數據和讀數據之間的狀態轉移。在每一個狀態下給出LCD顯示數據及控制信號,如片選、所寫數據/指令等。本文引用地址:http://www.j9360.com/article/202523.htm

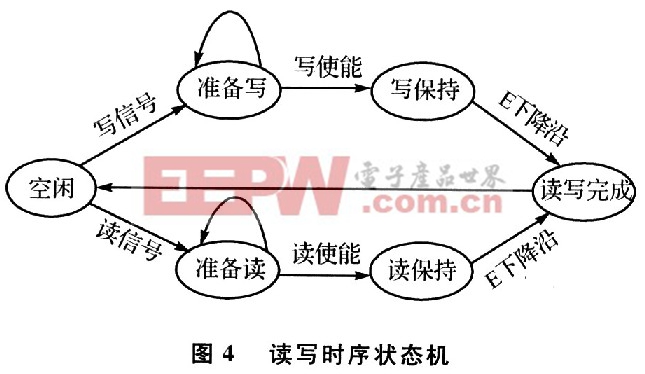

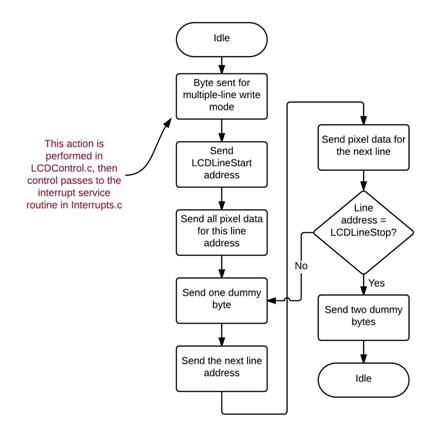

如圖4所示,讀寫時序狀態機用于控制讀或者寫外設的時刻,當讀寫完成時給出讀寫完成信號。其中,讀寫信號由圖2中的讀寫操作給出。根據CBGl28064讀寫時序要求,當R/W為高電平時,讀取顯示RAM中的數據;當R/W為低電平且在E的下降沿時,向顯示RAM中寫入數據。讀寫時序狀態機的讀寫信號由讀寫控制狀態機給定,其中,E為模塊使能信號。

3.2 寄存器組

寄存器組由一系列寄存器組成,為軟件提供了訪問硬件的通道。寄存器組中的寄存器是根據任務邏輯中需要實現的特定邏輯功能來設定的,任務邏輯中的數據通過這些寄存器傳輸。本設計中,寄存器組設定了8位頁地址寄存器、8位列地址寄存器,以及32位數據寄存器等。

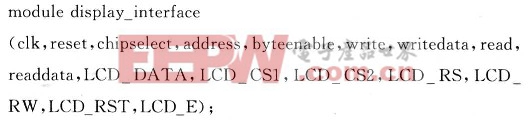

3.3 Ayalon總線接口

顯示驅動的Avalon總線接口需要一個簡單的Slave端口。該端口使用較少的Avalon信號來處理簡單的寄存器讀/寫傳輸。該模塊是與Avalon總線接口的一個頂層模塊,主要功能是對任務邏輯模塊和寄存器模塊進行例化和封裝,使其信號類型符合Avalon總線信號規范和外接模塊的信號規范。頂層接口定義如下:

3.4 顯示驅動封裝及軟件設計

直接在SOPC Builder中添加設計好的顯示驅動IP Core和Verilog HDL語言描述的文件,并根據Avalon總線傳輸規范設置好相關的信號線及傳輸參數。由于是在NiosII IDE環境下直接編寫用戶程序,可以不用編寫驅動程序。完成后,將顯示驅動IP Core添加至SOPC工程,并編譯、下載到FPGA器件中。

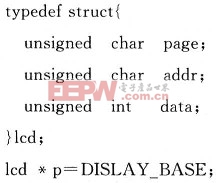

在NiosII IDE環境下,使用自己添加的模塊編寫程序,可直接調用甬數IOWR(BASE,OFFSET,DATA)和IORD(BASE,OFFSET)對內部寄存器進行讀寫。本文使用結構體定義了一個指向模塊的結構體指針,對寄存器進行讀寫操作。

CBGl28064本身不帶字庫,可以通過2種方式添加字庫:一種是把所需字庫做到硬件ROM中,增加了硬件資源成本,且缺乏靈活性;另一種是在軟件中定義字庫,通過寫數據寄存器進行顯示。本設計采用第2種方式,在軟件中定義字庫,并編寫了簡單的顯示測試程序,在液晶屏上顯示“ZHONG GUO”字樣。測試結果表明,該設計是正確可行的。此外,利用字模軟件生成的圖形數據,也可進行圖形顯示。

結語

本文采用有限狀態機設計了CBGl28064液晶模塊驅動硬件邏輯,并將顯示驅動IP核進行封裝構成了一個模塊化的獨立元件,使其能夠在其他的工程中復用;在此基礎上,基于NiosII嵌入式處理器構建了一個用戶定制的片上系統。經過在Cyclone系列FPGA上測試,該驅動能夠在C-BGl28064液晶模塊上顯示字符、圖形。整個系統體現了SOPC嵌入式系統的靈活性和擴展性。

評論