拿起手術刀 深入剖解路由器的“心臟”技術

選路機制實際上就是如何查找路由表,通過查詢路由表來決定向哪個方向轉發數據。一般來說,路由器首先搜索匹配的主機地址:如果沒有,再搜索匹配的網絡地址:最后搜索默認路由。一旦查到匹配的表項,路由器就會把數據從相應的接口發送出去。

路由器具備了上述各要素后,就可以完成數據轉發任務了。另外,路由器不僅負責對IP包的轉發,還要負責與別的路由器進行聯絡,共同確定互聯網的路由選擇和路由表的更新維護。

2、SOHO路由器原理

當內部計算機要與外部Internet網絡進行通信時,各內部間通過私有IP地址進行通信的計算機必須把私有IP地址轉換成合法IP。這種網絡地址轉換技術稱為NAT(Network Address Translation,網絡地址轉換)。在一個實際的私有網絡中,NAT功能通常內建在路由器、防火墻或獨立的NAT設備之上,網絡中的主機將這些設備作為自己的默認網關。通過這樣的配置,每一臺內部主機發送往Internet的數據報就會送到具有NAT功能的設備中進行轉換。NAT是SOHO路由器的必備功能,它是為解決IPv4地址不夠分配的矛盾而產生的一個簡單高效的解決方案。它能將任何兩個地址域的地址進行轉換,使私有網絡中多臺主機共享一個合法IP地址訪問Internet。

嵌入式路由器硬件系統介紹

1、硬件系統總體結構

硬件結構是非常重要的部分,因為我們拆開一個路由器后首先看到的、所能看到的也就是硬件結構,我們就舉例簡單介紹一下硬件設計的各個部位的細節內容。

為了宏觀查看,我們給出交換式寬帶路由器的硬件設計實例圖一張。圖中主要分為兩部分:

ARM4510B部分和交換芯片RTL8305部分,前者主要見上半圖,后者為下半圖。還有電源及各自的復位電路。

ARM4510B部分中,中央處理芯片為帶有網絡接口的S3C4510B--16/32位RISC微控制器,根據嵌入式操作系統的運行需要,擴展了SDRAM存儲器和Flash存儲器。SDRAM存儲器由兩片4X1MX16位的HY57V641620HGT

組成,作為嵌入式操作系統內核及應該程序運行的內存空間。Flash存儲器由一片1MX16位的SS139VF160組成,作為內核映像的存儲,并在嵌入式操作系統啟動時加載系統內核及程序。根據調試程序及燒寫Flash存儲器的需要,引出JTAG接口。根據顯示調試和運行信息的需要,提供了RS232接口。交換芯片 RTL8305部分中,提供4個LAN口(PORTO--PORT3)通過一四口的網絡隔離變壓器連接一個四口RJ45口,每個口可連接到10/10013aseT以太網,各端口之間有交換功能:還有一個WAN接口(CPO RT4)通過一單口的隔離變壓器連接RJ45口。根據顯示連接速度、狀態和電源等需要,接出LED燈進行顯示。根據交換芯片的管理需要,提供一串行EEPROM 24C01電路接口。根據交換芯片的主電源為2.5V.提供一個3.3V到2.5V的轉換器。

中央處理芯片通過MR(獨立媒體接口)接口與交換芯片RTL8035SB的PORT4的Mil接口相聯,將交換芯片的PORT4配置為物理層接收器。

當各部分電路設計完成后,形成硬件連接圖,進而焊接之后,就可以作為開發用的實驗硬件板了。下面就簡要介紹一下個硬件電路部分。

2、硬件系統的簡要設計介紹

⑴ARM處理器系統設計介紹

①S304510B概述

Samsung公司的S34510B是基于以太網應用系統的高性價比的16/32位RISC微控制器,內含一個由ARM公司設計的16/32位的ARM7TDMI RISC處理器核。ARM7TDMI為低功耗,高性能的16/32位核。

除了ARM7TDMI外,該芯片還有一些片內外圍功能模塊,主要為: 內部RAM (8Kbyte unified cache/SRAM),I2 C接口電路(I2C interface)、以太網控件器(Ethernetco ntroller),HDLC,GDMA、串口(UART),時鐘(Timers)、可編程1/O口(Programmable I/O ports)及中斷控件器(Interrupt controller)等。

S3C4510B結構框圖所示。在實際運行過程中最主要用到的部分為:以太網接口及串口部分,前者用于收發以太包,后者主要作為操作系統調試接口。

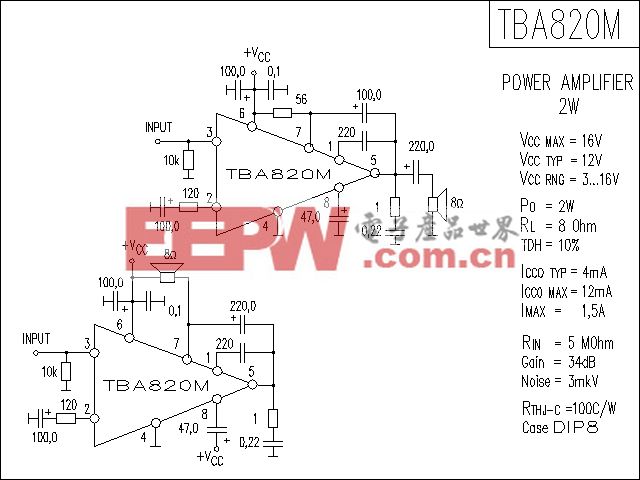

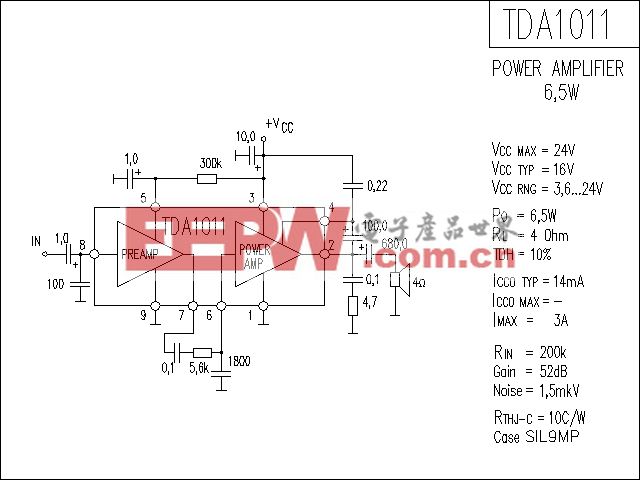

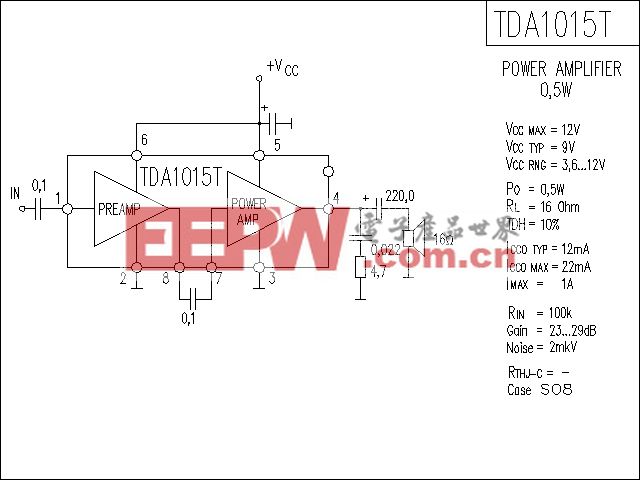

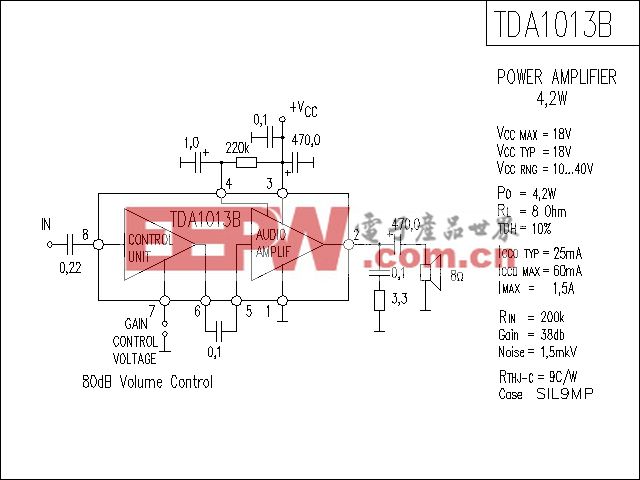

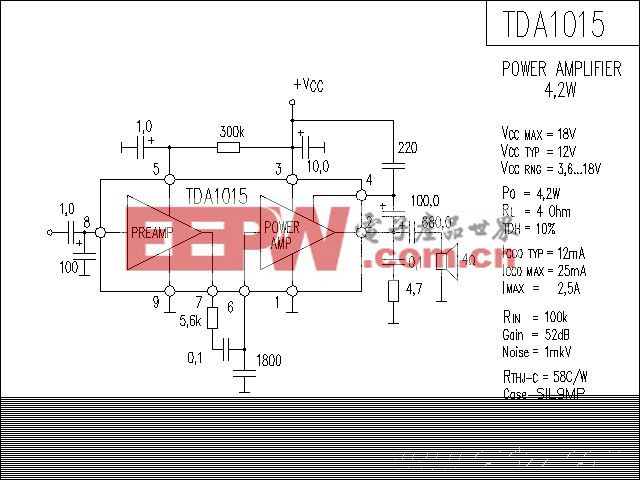

②ARM 處理器系統電源電路和復位電路

主要是實現供電和復位功能,電路部分不做詳細講解,有深入研究需要的愛好者可以查看相關的電子相關參考資料進行深入學習。為使文章通俗易懂,以下各電路部分也是做一宏觀介紹,細節部分包括電路布線等不再深入講解。

③ARM處理器與Flash存儲器接口電路

讀者只要知道這部分的電路連接是為實現能在Flash存儲器編寫程序即可。

④ARM處理器與SDRAM接口電路設計介紹

與 Flash存儲器相比,SDRAM不具有掉電保持數據的特性,但其存儲速度大大高于Flash存儲器,且具有讀/寫屬性。因此SDRAM在系統中主要用于程序的運于空間、數據及堆棧。當系統啟動時,CPU首先從復位地址0x0片讀取啟動代碼,在完成系統的初始化后,程序代碼調入SDRAM中運行,以提高系統的運行速度。

SDRAM 具有單位空間存儲量大和價格便宜的特點,廣泛用于各種嵌入式系統中。SDRAM 的存儲單元可以理解為一個電容,總是傾向于放電,為了避免數據丟失,必須定時刷新(充電)。因此,在系統中使用SDRAM,就要求微處理器有刷新的控制邏輯或者在系統中另外加刷新控制邏輯電路。S3C4510B在片內具有獨立的SDRAM刷新控制邏輯,可以方便的與SDRAM接口。

⑤ARM處理器串行接口電路設計介紹

幾乎所有的微控件器、PC都提供串行接口,使用美國電子工業協會(EIA)推薦的RS-232-C接口標準,這是一個很常用的串行數據傳輸總線接口標準。早期被用于計算機和終端通過電話線和MODEM進行遠距離的數據傳輸,隨著微型計算機和微控制器的發展,不僅在遠距離,近距離也采用了該通信方式。在近距離的通信中不采用電話線和MODEM,而是直接進行端到端的連接。

RS-232-C標準采用的是9芯或是25芯的D型插頭。

⑥ARM處理器JTAG接口電路設計介紹

JTAG(JointTe stAc tionG roup,聯合測試行動小組)是一種國際標準測試協議,主要用于芯片內部測試及系統進行仿真、調試。JTAG是一種嵌入式調試技術,它在芯片內部封裝了TAP(Test Access Port,測試訪問接口),通過專用的JTAG測試工具對內部節點進行測試.標準的JTAG接口是四線:TMS、TCK、TDI、TDO,分別為測試模式選擇、測試時鐘、測試數據輸入、測試數據輸出。JTAG測試允許多個器件通過JTAG接口串聯在一起,形成一個JTAG鏈,能實現以各個器件分別測試。JTAG接口還常用于ISP(In System Programmable)功能,如對Flash器件進行編程。

評論