盤點RS485收發連接器參考電路設計

555定時器為邊沿觸發,當TxD發送高電平時,555定時器OUT引腳輸出低電平,當TxD發送低電平時,555定時器OUT引腳輸出高電平,當TxD轉為高電平時,OUT引腳輸出的高電平狀態會延遲一會再轉入低電平,以確保發送數據的正確性。

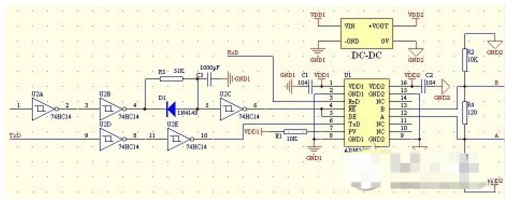

采用74HC14和RC電路實現,此電路是對單純使用74HC14實現自收發電路的改進,增加了RC充放電電路,減少總線處于空閑狀態的時間,電路如下圖:

當TxD信號為高電平,則通過電阻為電容充電,其充電時間為T,該時間應設置為串口發送一個字節所需要的時間,由R,C參數來確定。當電容充滿后,則DE/RE為低電平,使ADM2483處于接收狀態。在發送數據時,TxD起始位產生第一個下降沿,使電容經過二極管進行快速放電,使DE/RE很快變為高電平,ADM2483處于發送狀態。在發送過程中, 當TxD變成高電平時,電容通過電阻緩慢充電,使DE/RE仍然保持在發送狀態,可有效吸收總線上的反射信號。當RC充電結束,使DE/RE轉入接受狀態時, 總線上的上拉、下拉電阻將維持TxD高電平的發送狀態,直至整個bit發送結束。

當數據發送完畢以后,TxD變為高電平,RC又開始充電,即經T時間后,ADM2483又轉換為接收狀態。以上所有電路均為參考電路,為電路設計者提供思路,在實際使用中請再次驗證,以確保電路的穩定及不會對系統造成破壞。對于電路損壞造成的損失,概不負責。

評論