一篇文章說清半導體制程發展史

相比之下,目前的最小量產的晶體管尺寸是20nm (14nm node),已經有了10倍以上的差距。

本文引用地址:http://www.j9360.com/article/201707/361285.htm有人會問,為何沒有衍射效應呢?

答案是業界10多年來在光刻技術上投入了巨資,先后開發了各種魔改級別的暴力技術,諸如浸入式光刻(把光程放在某種液體里,因為光的折射率更高,而最小尺寸反比于折射率)、相位掩模(通過180度反向的方式來讓產生的衍射互相抵消,提高精確度),等等,就這樣一直撐到了現在,支持了60nm以來的所有技術節點的進步。

又有人會問,為何不用更小波長的光源呢?

答案是,工藝上暫時做不到。

是的,高端光刻機的光源,是世界級的工業難題。

以上就是目前主流的深紫外曝光技術(DUV)。業界普遍認為,7nm技術節點是它的極限了,甚至7nm都不一定能夠做到量產。下一代技術仍然在開發之中,被稱為極紫外(EUV),其光源降到了13nm。但是別高興地太早,因為在這個波長,已經沒有合適的介質可以用來折射光,構成必須的光路了,因此這個技術里面的光學設計,全部是反射,而在如此高的精度下,設計如此復雜的反射光路,本身就是難以想象的技術難題。

這還不算(已經能克服了),最難的還是光源,雖然可以產生所需的光線,但是強度遠低于工業生產的需求,造成EUV光刻機的晶圓產量達不到要求,換言之,拿來用就會賠本。一臺這種機器就上億美元。所以EUV還屬于未來。

基于以上三個原因,其實很早開始就導致晶體管的尺寸縮小進入了深水區,越來越難,到了22nm之后,已經無法做大按比例縮小了,因此就沒有再追求一定要縮小,反而是采用了更加優化的晶體管設計,配合CPU架構上的多核多線程等一系列技術,繼續為消費者提供相當于更新換代了的產品性能。

目前,技術節點的數字仍然在縮小,但是已然不再等同于晶體管的尺寸,而是代表一系列構成這個技術節點的指標的技術和工藝的總和。

第三個問題,技術節點的縮小過程中,晶體管的設計是怎樣發展的。

首先要搞清楚,晶體管設計的思路是什么。主要的無非兩點:第一提升開關響應度,第二降低漏電流。

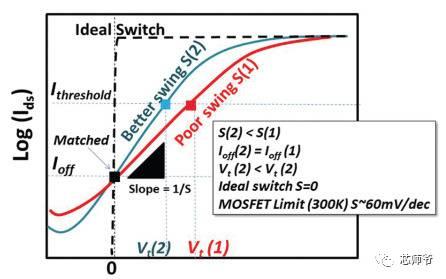

為了講清楚這個問題,最好的方法是看圖。晶體管物理的圖,基本上搞清楚一張就足夠了,就是漏電流-柵電壓的關系圖,比如下面這種:

橫軸代表柵電壓,縱軸代表漏電流,并且縱軸一般是對數坐標。

前面說過,柵電壓控制晶體管的開關。可以看出,最好的晶體管,是那種能夠在很小的柵電壓變化內,一下子就從完全關閉(漏電流為0),變成完全打開(漏電流達到飽和值),也就是虛線。這個性質有多方面的好處,下面會說明。

顯然這種晶體管不存在于這個星球上。原因是,在經典的晶體管物理理論下,衡量這個開關響應能力的標準,叫做Subthreshold Swing(SS,不是黨衛軍...),有一個極限值,約為60,背后的原因就不細說了。

根據英特爾的數據,最新的14nm晶體管,這個數值大概是70左右(越低越好)。

并且,降低這個值,和降低漏電流、提升工作電流(提高速度)、降低功耗等要求,是等同的,因為這個值越低,在同樣的電壓下,漏電流就越低。而為了達到同樣的工作電流,需要的電壓就越低,這樣等同于降低了功耗。所以說這個值是晶體管設計里面最重要的指標,不過分。

圍繞這個指標,以及背后的晶體管性能設計的幾個目標,大家都做了哪些事情呢?

先看工業界,畢竟實踐是檢驗真理的唯一標準。下面是我的記憶,和節點的對應不一定完全準確,但具體的描述應該沒錯:

65nm引入Ge strained溝道。

strain我不知道如何翻譯成中文詞匯,但是其原理是通過在適當的地方摻雜一點點的鍺到硅里面去,鍺和硅的晶格常數不同,因此會導致硅的晶格形狀改變,而根據能帶論,這個改變可以在溝道的方向上提高電子的遷移率,而遷移率高,就會提高晶體管的工作電流。而在實際中,人們發現,這種方法對于空穴型溝道的晶體管(pmos),比對電子型溝道的晶體管(nmos),更加有效。

45nm引入了高k值絕緣層/金屬柵極配置。

這個也是一個里程碑的成果,我在念書的時候曾經有一位幫他搬過磚的教授,當年是在英特爾開發了這項技術的團隊的主要成員之一,因此對這一點提的特別多,耳濡目染就記住了。

這是兩項技術,但其實都是為了解決同一個問題:即在很小的尺寸下,如何保證柵極有效的工作。

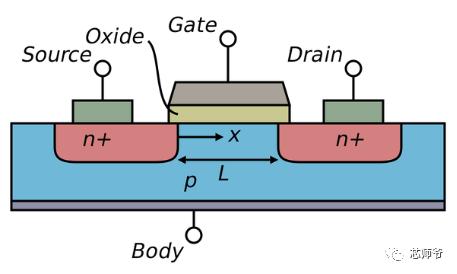

前面沒有細說晶體管的結構,下面補一張圖:

這是一個最基本的晶體管的結構示意圖,現在的晶體管早就不長這樣了,但是任何半導體物理都是從這兒開始講起的,所以這是“標配版”的晶體管,又被稱為體硅(bulk)晶體管。

gate就是柵。

其中有一個oxide,絕緣層,前面沒有提到,但是卻是晶體管所有的構件中,最關鍵的一個。它的作用是隔絕柵極和溝道。因為柵極開關溝道,是通過電場進行的,電場的產生又是通過在柵極上加一定的電壓來實現的,但是歐姆定律告訴我們,有電壓就有電流。如果有電流從柵極流進了溝道,那么還談什么開關?早就漏了。

所以需要絕緣層。為什么叫oxide(or dielectric)而不叫insulator呢?因為最早的絕緣層就是和硅非常自然地共處的二氧化硅,其相對介電常數(衡量絕緣性的,越高,對晶體管性能來說,越好)約是3.9。一個好的絕緣層是晶體管的生命線,這個“好”的定義在這里不多說了,但是要說明,硅天然就具有這么一個性能:超級好的絕緣層,對于半導體工業來說,是一件有歷史意義的事情。

有人曾經感慨,說上帝都在幫助人類發明集成電路,首先給了那么多的沙子(硅晶圓的原料),又給了一個完美的自然絕緣層。所以至今,硅極其難被取代,一個重要原因就是,作為制造晶體管的材料,其綜合性能太完美了。

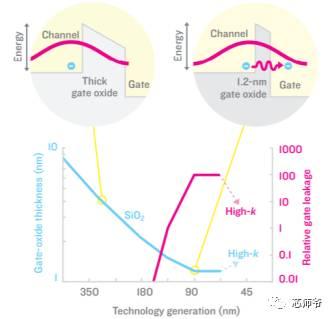

二氧化硅雖好,在尺寸縮小到一定限度時,也出現了問題。別忘了縮小的過程中,電場強度是保持不變的,在這樣的情況下,從能帶的角度看,因為電子的波動性,如果絕緣層很窄很窄的話,那么有一定的幾率電子會發生隧穿效應而越過絕緣層的能帶勢壘,產生漏電流。

可以想象為穿過一堵比自己高的墻。這個電流的大小和絕緣層的厚度,以及絕緣層的“勢壘高度”,成負相關。因此厚度越小,勢壘越低,這個漏電流越大,對晶體管越不利。

另一方面,晶體管的開關性能、工作電流等,都需要擁有一個很大的絕緣層電容。實際上,如果這個電容無限大的話,那么就會達到理想化的60的那個SS指標。

這里說的電容都是指單位面積的電容。這個電容等于介電常數除以絕緣層的厚度。顯然,厚度越小,介電常數越大,對晶體管越有利。

可以看出,這里已經出現了一對設計目標上的矛盾,那就是絕緣層的厚度要不要繼續縮小。實際上在這個節點之前,二氧化硅已經縮小到了不到兩個納米的厚度,也就是十幾個原子層的厚度,漏電流的問題已經取代了性能的問題,成為頭號大敵。

于是聰明絕頂的人類開始想辦法。人類很貪心的,既不愿意放棄大電容的性能增強,又不愿意冒漏電的風險。于是人類說,如果有一種材料,介電常數很高,同時能帶勢壘也很高,那么是不是就可以在厚度不縮小的情況下(保護漏電流),繼續提升電容(提高開關性能)呢?

于是大家就開始找,用幾乎暴力的方法,找了許多種奇奇怪怪的材料,終于最后經過驗證,確定使用一種名為HfO2的材料。這個元素我以前聽都沒有聽過,中文念什么我都說不上來。就是這么牛。這個就叫做high-k,這里的k是相對介電常數(相對于二氧化硅的而言)。

當然,這個工藝的復雜程度,遠遠超過這里描述的這么簡單。具備high-k性質的材料很多,但是最終被采用的材料,一定要具備許多優秀的電學性質,因為二氧化硅真的是一項非常完美的晶體管絕緣層材料,而且制造工藝流程和集成電路的其它制造步驟可以方便地整合,所以找到這樣一項各方面都符合半導體工藝制造的要求的高性能絕緣層材料,是一件了不起的工程成就。

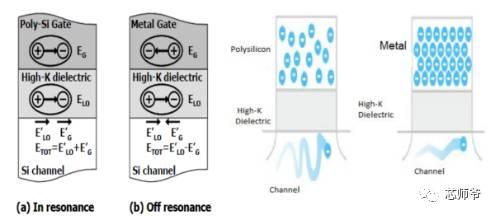

至于金屬柵,是與high-k配套的一項技術。在晶體管的最早期,柵極是用鋁制作,后來經過發展,改用重摻雜多晶硅制作,因為工藝簡單,性能好。到了high-k這里,大家發現,high-k材料有兩個副作用,一是會莫名其妙地降低工作電流,二是會改變晶體管的閾值電壓。閾值電壓就是把晶體管的溝道打開所需要的最小電壓值,這個值是非常重要的晶體管參數。

這個原理不細說了(其實是說不清楚才對吧哈哈...?),主要原因是,high-k材料會降低溝內的道載流子遷移率,并且影響在界面上的費米能級的位置。載流子遷移率越低,工作電流就越低,而所謂的費米能級,是從能帶論的圖像上來解釋半導體電子分布的一種分析方法,簡單地說,它的位置會影響晶體管的閾值電壓。

這兩個問題的產生,都和high-k材料內部的偶極子分布有關。偶極子是一端正電荷一端負電荷的一對電荷系統,可以隨著外加電場的方向而改變自己的分布,high-k材料的介電常數之所以高的原因,就跟內部的偶極子有很大關系。所以這是一把雙刃劍。

于是人類又想,就想到了用金屬做柵極,因為金屬的自由電荷濃度極高(超過10^20),而且有鏡像電荷效應,可以中和掉high-k材料的絕緣層里的偶極子對溝道和費米能級的影響。這樣一來就兩全其美啦。

至于這種或這幾種金屬究竟是什么,很抱歉,除了掌握技術的那幾家企業之外,外界沒有人知道,是商業機密。

評論