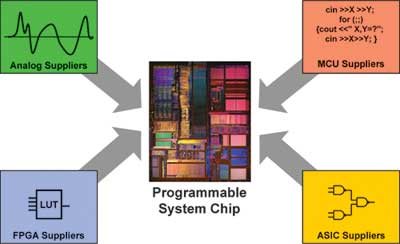

可編程系統芯片解決方案的三個關鍵問題(圖)

除了要為客戶提供更多的功能,這些供應商還希望能降低開發成本。但是,掩模成本的不斷攀升將繼續限制ASIC產品的開發,并且也會影響MCU和模擬器件供應商擴大產品種類。為產品增加可編程和可配置的能力,能讓半導體供應商只需以更少的掩模組合便可為相同的應用領域服務,從而縮短開發周期和降低開發成本。

在現有的四種主流技術(MCU、模擬電路、ASIC和FPGA)中,FPGA的可編程能力可謂占盡優勢,但還必須克服一些障礙才能開發成功的方案。FPGA技術的開發需要龐大的軟、硬件投資。硬件芯片的要求包括開發高效、靈活和高性能的可編程架構,并需要廣泛的軟件工具以支持設計開發、驗證、評測和編程。

|

| 圖1 實現可編程系統芯片(PSC)解決方案的方式 |

與FPGA IP不同,ASIC庫可通過代工方式獲得,而市場上有各種各樣的MCU內核可供授權使用。這個領域里有幾家做得很成功的公司,其中最著名的是ARM。此外,模擬IP也可從多家供應商購得或自行開發。

三個關鍵因素

要實現可編程系統芯片有三個關鍵:首先是工藝技術,其次是系統設計構架,最后是工具支持。

工藝技術的優劣是在單個單芯片上集成存儲器、模擬和可編程邏輯的一個最大關鍵,目前一般采用標準CMOS工藝。由于需要高門數來實現大型可編程邏輯芯片,許多FPGA供應商均采用最尖端的CMOS技術。但是,CMOS工藝并不適用于嵌入式Flash和模擬集成,因此可編程系統芯片無法采用標準的CMOS工藝。通常,嵌入式Flash和模擬器件的工藝支持是尖端的CMOS節點背后的多個工藝節點。尖端、高門數器件和以模擬及Flash為基礎器件之間的工藝仍存在鴻溝。

許多模擬器件會與外界的傳感器或電源接口,外界信號的電壓不會都是90nm CMOS工藝技術規定的1.2V電壓。優良的可編程系統芯片工藝將會支持模擬器件與這些信號的直接連接。通過支持較高的電壓,先進的Flash工藝便可擴大集成模擬IP的動態電壓范В傭錘叩男旁氡群透訓哪D廡閱堋N思醯陀篩咚偈致嘸諛D釯P中加入的噪聲,嵌入式Flash工藝必須與模擬和數字部分有效地隔離開來。這個工藝還必須支持高性能RAM和邏輯功能。

以Flash為基礎的FPGA必須能處理編程所需的大電壓,并且很好地進行隔離,以及對這些電壓加以控制。高電壓晶體管提供很大的動態電壓范圍,以及能與模擬IP的高電壓信號直接連接。此外,三井技術會提高模擬和數字元件之間的隔離度,有助于減小芯片尺寸。

相對于混合信號AISC的開發或更復雜的多芯片方案而言,可編程系統芯片的一個關鍵優勢是其產品推出市場的時間較短。為了充分發揮這一優勢,系統設計必須好好地加以組織,讓用戶能根據需求在高或低抽象度的水平下進行開發和設計。

可編程系統芯片技術為系統設計人員提供的靈活性可以由類似于OSI通信層的多層設計抽象水平顯示出來。

這個層次模型提供了靈活的設計環境,可同時在高和低的抽象水平進行設計。可編程系統芯片堆棧有4個層次。0層類似于物理層,包括硬模擬IP和軟及/或硬數字IP。第1層控制與0層及0層中各部件之間的通信,與數據鏈路層類似。第2層很像OSI的表述層,負責將數據帶到一個端點,使到最終系統應用(第3層)可以在其上工作,就像應用層一樣。

0層即外設層(物理層)是可配置的功能塊,可以采用硬連接結構,如PLL(鎖相環)或模擬輸入通道,也可以在軟門電路上實現,如UART或PC接口。這些外設可以配置,并支持標準接口以便利通信和執行。

第1層主干(鏈路層)連接和控制外設的存取。這應該采用軟門電路結構,可延展至任何規模的外設。主干層是總線和控制邏輯,負責管理外設配置,以確保其運作正常。主干層還借助通用的外設接口和低層次狀態機,使外設管理能從系統設計中有效地卸除出來。主干層還能根據外設行為和定義的性能規范,對閾限標識進行置位和清零。可編程系統芯片堆棧的靈活性允許設計人員直接配置外設,并且可按需要越過主干層,如這是所需的控制水平的話。

|

| 圖2 可編程系統芯片(PSC)技術的層次 |

第2層小型應用附屬程序Applet(表述層)是獨立的應用建構模塊,利用Flash和模擬外設實現FPGA門電路內指定的功能。小型應用附屬程序通過與主干通信對激勵信號和板級事件做出響應;即通過主干存取和操作外設,對激勵信號做出響應或發起其他動作。作為可完全重復使用的IP結構,小型應用附屬程序能輕松導入設計環境及從設計環境中導出。這樣,設計人員就可迅速在其設計中導入多個小型應用附屬程序,從而構建復雜的設計。

第3層系統應用程序(應用層)是較大的用戶應用程序,采用了一個或以上小型應用附屬程序。由于在最高的抽象水平進行設計,并且由可編程系統芯片技術堆棧予以支持,因此整個FPGA系統設計無須任何HDL(硬件描述語言)代碼便可設計出來。該應用程序在FPGA門電路中實現,只要導入和配置多項小型應用附屬程序即可生成。

用戶還可選配軟MCU內核,以實現基于軟件和HDL設計方法的組合。系統的劃分非常靈活,可讓MCU置于小型應用附屬程序之上,或在需要時吸收小型應用附屬程序或小型應用附屬程序與主干。

可編程系統芯片技術堆棧提供了非常靈活的設計環境示例。這種構架使用戶可以獲得最大的設計靈活性,從最高水平的“選與點”設計(可實現快速的應用開發)到極低層次的設計(能實現最高的設計控制)以及兩者之間的水平。

支持工具

整合復雜可編程系統芯片的工具會帶來新的復雜性和需求。在這層面所要求的開發工具特性如下:

高水平的設計能力;

快速生成應用程序的新方法;

軟/硬件協同驗證;

以總線為基礎的通信;

器件/系統建模及設計劃分;

創新的調試功能。

為了支持這種高水平的集成,開發工具必須協調配合。半導體器件和設計環境必須協調一致,從而達到事半功倍的產品開發效率。對設計人員來說,盡管添加了混合信號和Flash功能,可編程系統芯片環境下的設計工作應當與數字設計流程環境一樣流暢簡明。

這些新工具必須能讓設計人員在設計中輕松執行和配置外設、在外設之間建立連接、創建或導入構件模塊或參考設計,以及進行軟/硬件驗證。這些工具套件還應包含全面的軟/硬件調試功能及整套實用程序,以簡化基于軟處理器內核嵌入式解決方案的開發工作 (如ARM和8051)。

可編程系統芯片工具組必須為用戶提供軟/硬件設計中的高度靈活性,以便進行系統建模。設計工程師和系統工程師能在FPGA邏輯門上自由劃分其應用,也可通過選配軟處理器內核或透過軟、硬件結合的方式在軟件中執行。

設計生成工具必須提供非常靈活的環境以及多種選項。只要有足夠的FPGA邏輯門資源,用戶便能在設計環境中導入任何數量的小型應用附屬程序。由圖形用戶界面支持,這些小型應用附屬程序可以在設計及不同的外設中實現,只需單擊鼠標便可進行所有配置,過程中完全無須HDL編碼。與此同時,該工具鏈還會創建主干,連接所需的外設,以及生成低層處理所需的控制。所有這些都會在后臺自動完成,無須用戶直接介入。這些以圖形用戶界面為基礎的工具使用容易,而且提供快速的設計開發。這些工具并不排斥傳統的HDL編碼開發,讓習慣于這種開發流程的用戶也可采用HDL編碼來按需要連接各個門電路,或實現高度定制化的設計。

由于可編程系統芯片技術增加了復雜性和前所未有的集成度,仿真因此在設計驗證中扮演舉足輕重的角色。混合信號元件可在數字邏輯中進行行為化模型,并在數字環境中驗證。可編程系統芯片工具解決方案必須提供整套數字化行為仿真模型,對所有集成在芯片上的各種資源給予仿真支持。這個策略能大幅降低工具成本,因為它不再需要昂貴的模擬建模工具,而能夠有效實現系統級仿真的模擬建模工具一般高達10萬美元。

由用戶或應用生成器創建的RTL應可順利地通過邏輯及物理綜合。可編程系統芯片技術提供優異的集成能力,為單芯片設計的驗證帶來很大挑戰。因此,必須采用先進的調試工具在堆棧中各個應用抽象層面進行設計驗證。例如,用戶應可在應用指定的模塊中嵌入邏輯分析器,以實現實時傳感功能;并且還可將這些分析器與主干接口,實時地監控外設的活動。此外,還需要額外的調試功能來讓用戶存取和修訂與外設、寄存器列、嵌入式SRAM和Flash內存有關的配置。

由于可編程系統芯片平臺支持嵌入式處理解決方案,因此也必須支持流行的內核,如8051和ARM7,才能實現最廣泛的應用。由Actel和其他供應商提供的工具能協助用戶用C語言構建應用,且特為可編程系統芯片器件上運行的軟MCU而優化。用戶可利用其軟件調試工具調試程序代碼,并在協同仿真的環境下執行指令集仿真。

設計團隊非常需要開放式的設計環境。這種設計環境能促進技術生態系統的發展,使客戶、用戶群、第三方工具開發商和設計公司能夠聯結一起,形成互動。其中,每一位成員只需專注于自己所長,即可創造出一個高效和低成本的開發環境。系統設計人員能夠從生態系統掌握所需的資源。

可編程系統芯片技術和設計開發環境能讓用戶在高抽象度的層面進行設計,并且輕易導入和導出小型應用附屬程序。這些模塊化和已定義的小型應用附屬程序更有助于IP的重復使用和共享。客戶可開發小型應用附屬程序以支持其應用,也可以將其混合、匹配和內部共享。第三方工具供應商可針對特定的縱向市場應用開發小型應用附屬程序生成器,又或采用模型將小型應用附屬程序生成器作為工具鏈的一部分分發出去,從而加快設計開發。此外,系統設計人員還可結合處理器/微控制器生態系統,與多個解決方案供應商共同協作。

總結

由于在有效性、易用性和成本效益上的固有優勢,FPGA供應商更容易開發可編程系統芯片解決方案。設計架構決定了是否能縮短開發周期和降低開發成本,保持高度的靈活性,以滿足不同用戶群的各種需求。

采用類似于OSI網絡堆棧的開發環境能夠簡化開發流程,讓傳統的數字設計人員依照習慣在低層進行設計;至于非傳統的FPGA設計人員則可通過導入和配置小型應用附屬程序,在較高層次進行設計。對于熟悉嵌入式處理器的設計人員來說,可以利用熟悉的C編碼并在軟件中進行全盤設計。該模型還提供各種靈活的結構化手段,充分發揮高集成水平,便利于IP的重復使用和加快設計開發。

評論