剖析:ADC設計全接觸

新的應用需求不斷推動模擬技術的發展:性能越來越高,集成度不斷提高。ADC產品作為模擬IC的重要成員,在符合上述發展的趨勢下,還存在自身的特點……

當看到那小小的騎車機器人“村田頑童”可以前進、倒退、爬坡并且停而不倒時,你是否知道其中使用了多種傳感器以檢測各個方向的傾斜角度和探測道路狀況;當 你驚嘆殘疾人可以自如地控制假肢完成復雜動作時,你是否知道與假肢相連的探測器可以檢測人體肌肉的最細微運動從而實現對假肢的控制;也許你并沒有留意到用 手機通話時顯示屏會自動關閉以便降低功耗,這是手機檢測到顯示屏被物體(例如耳朵)遮住時的操作……所有這些都表明:用戶體驗推動半導體和技術創新的進 步,并在同時對模擬IC的性能提出更高要求。

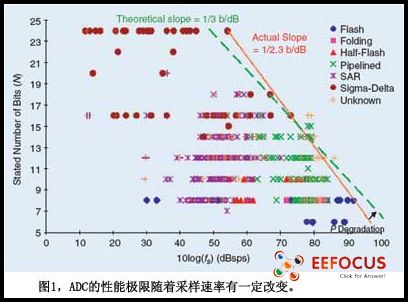

ADC的性能極限隨著采樣速率有一定改變

同時,電子器件的集成度越來越高,例如AD9271在單一芯片上集成了一個完整的8通道超聲接收器,其中的一個通道就包含低噪聲放大器(LNA)、可變增益放大器(VGA)、抗混疊濾波器(AAF)和12位 ADC。

雖 然集成是大趨勢,但是還需要考慮成本,客戶需要,技術要求,工藝發展等諸多因素。ADI大中國區資深業務經理周文勝說,“當性能指標要求特別高時,采用集 成的方案并不明智;市場上需要什么樣的芯片,芯片供應商就應該為實現這個系統去做一些相應的設計,ADI的‘智能分割’概念就是強調哪些功能模塊應該集 成,哪些功能模塊要分開放,最終使設計達到最符合客戶的要求,也符合技術要求。把所有的芯片集成在一起,當工藝都一樣時,整體 BOM可以降低;但當各芯片工藝不一樣時,如果硬要把它們集成在一起可能會造成整個BOM上升。”

模數轉換器(ADC) 作為模擬IC的一種,也同樣順應上述模擬IC的發展趨勢,但是它還遵循自身發展的規律。從最初的11位分辨率、50 kSps采樣速率和500 W功耗的SAR型ADC到現在的16位分辨率、1MSps采樣速率并且僅7 mW功耗的ADC AD7980, ADC的性能已經取得了巨大進步。現有ADC存在7種結構:falsh, half-flash, folding, SAR, pipelined, sigma-delta和未知結構。其中piplined和未知結構具有最佳的整體性能,所以它們非常適合例如無線收發器應用和軍用等高性能要求的應用;SAR ADC具有最寬的采樣速率,雖然它不是最快的,但由于低成本和低功耗使其很受歡迎。Sigma-delta ADC具有最高的分辨率,但是采樣速度較低,從kSps到MSps;而flash ADC由于其并行結構具有最高采樣速率可達GSps,但是由于非線性使其分辨率限制在8位以內。

在 進行ADC性能比較時通常使用品質因數:P=2B×fs和F=(2B×fs)/Pdiss,其中B是SNR比特數,fs是采樣速率;Pdiss是功耗。文 獻1認為,在開發高功率效率的ADC設計上取得了顯著進步,但是,ADC的分辨率和速度的乘積P在1993年~1999年的6年中幾乎沒有進步。文獻 [2]針對4家主要IC制造商(ADI, Maxim, NS和TI)的ADC產品的3個通用性能指標(采樣速率、分辨率和功耗)分析后認為:上述P并不是恒定的,而是在低采樣速率下部分P有一些改善;在高采樣 速率下部分P有一定降低(見圖1)。

Sigma- delta和flash轉換器是上述7中結構中僅有的F隨時間降低的兩種結構。這兩種ADC針對特定要求,只有較窄的應用范圍,它們都需要犧牲更多的功耗 用于實現更高性能,這導致了F的降低。余下的SAR, pipelined等5種結構滿足速度和分辨率的中等應用要求,因而能獲得更高的F。二十多年來,ADC技術的發展一直被新應用推動,從而促進P的增加。 雖然UWB,OFDM和雷達系統等應用推動ADC性能極限發展,ADC設計的主要挑戰已經從性能擴展轉向降低功耗,這一挑戰在移動通信和SDR應用中尤為 突出。

ADI專家:寬帶ADC前端設計注意事項

評論