一文看懂3D晶體管

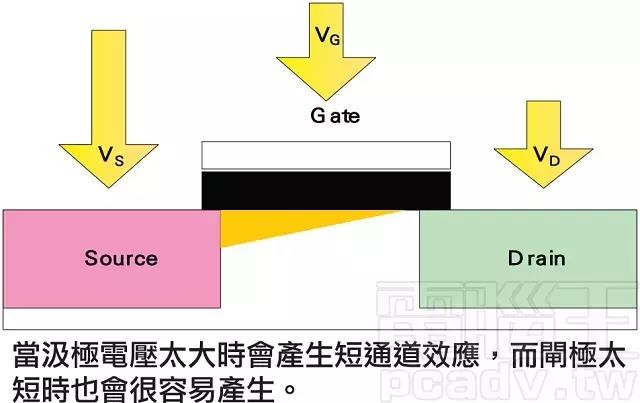

上圖是最近比較常用的MOS元件結構,我們可以發現和之前列出來的簡圖有不少差異,事實上增加的部份都是為了避免通道產生速度過慢、短通道效應、性能不良等等問題而來。但是這些解法也會帶來副作用,互相牽制以致沒有一個完美的解決方案。(不然大家趕著變成3D干嘛?)

本文引用地址:http://www.j9360.com/article/201611/339540.htm影響推動力的最主要因素還是來自于短通道效應,特別是本身就已經夠短的30nm閘極通道更容易發生。為了解決短通道效應,有人會預先在通道形成的部位加入雜質,使得原本的NP接面導通電壓下降。其原理就是讓P型半導體不要這么偏向P型,有點接近N型,但是這樣一來也造成了通道切斷時很可能會有漏電流,因為介面的能障變小,而且加入雜質會創造許多自由電子和電洞成對出現的機會。

▲短通道效應:通道提早縮水了

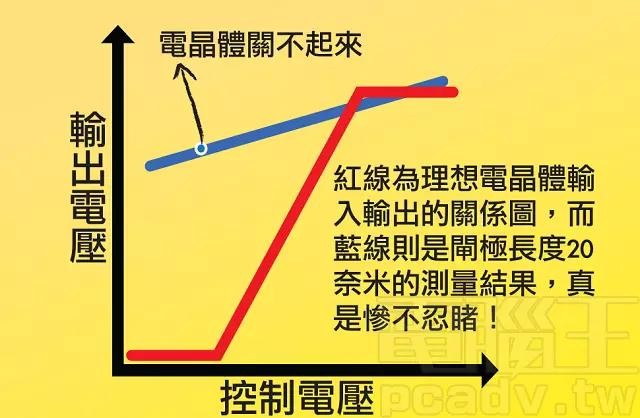

關不掉的晶體管

在沒有外部電場的情況下,這成對的電子和電洞因靜電力平衡會再度中和掉對方而消失;但是當有外部電場(源極有電壓的時候)時,這些隨機產生的電子就會變成額外的導電品,使得晶體管永遠關不起來。原本我們希望閘極在拉高電位一到飽和態后,晶體管就可以把源極的輸出降到零,現在辦不到了?這就叫做關閉態的漏電流。就算我們不加入雜質讓能障變小,當閘極電壓小于汲極電壓太多時,這個能障一樣會變小,在30nm以下的晶體管中產生漏電流的比例就會遠高于過去90nm或120nm的晶體管了。

▲關不起來的電壓

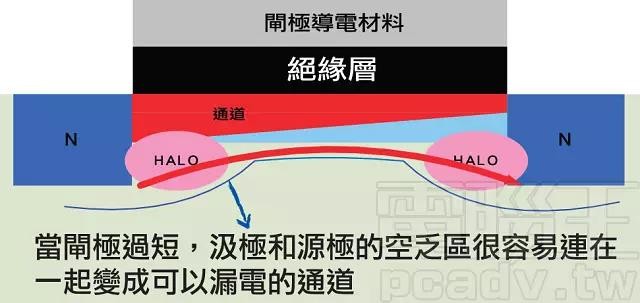

閘極太短的漏電流

▲閘極過短導致的漏電

在上圖中,我們又看到了另一種漏電流的產生原因,當我們的電場施加于3個極時,我們可以看到因靜電力之故,某些區域的電子、電洞都飄往源極以及汲極,并且閘極為了形成通道也會吸取中間部位大多的電子、電洞聚集到通道,這些被吸走電洞、電子的區域形成了空乏區,這空乏區沒什么能障,原本也沒什么作用,但是若是閘極通道很短就好玩了。

我們看到圖中的汲極到源極之間除了通道外全部被空乏區連起來了,任何不小心落入這空乏區的電荷都會被來自汲極的電場用力一推,就往源極跑出去了!(額外不受控制的電流輸出,又是一個漏電的來源)

推動力不足也可能是因為形成通道的電荷量就是不夠,造成通道太薄太小,如果我們使用增加晶體管寬度的方法解決這種問題,就會造成制造成本升高,但是如果增加通道形成區附近的雜質,又會漏電。所以最好的方法恐怕只有換一個晶體管結構了!

寄生電容

由于材料介接的影響,對于高頻訊號來說,原本良好的導體其實訊號跑起來并沒這么良好。會跑出訊號經過電容器一般的濾波效應,讓訊號變差,但是我們明明沒有在導體上面放電容器,這個電容效應是導體自發的物理現象,所以我們叫它寄生電容。

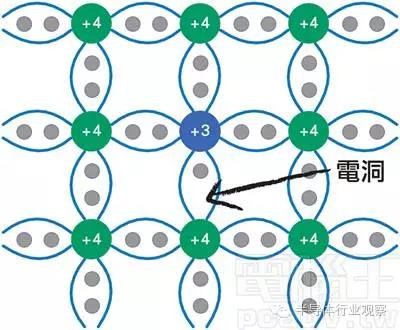

本征電子

就如同高中提到的酸堿平衡一樣,水的成分是氧化氫,但是就算是純水,其中也會固定解離出等量的氫離子和氫氧根離子。我們在材料中放進雜質以利產生電洞時,也會因熱效應而產生一些等量的電子和電洞,但是他們出現一下子就又會結合在一起了,就好像情人暫時分手但是馬上又復合一樣。而當某一對分手的電子電洞復合的時候,又會有另一對分手,所以材料中永遠會有一些自由電子,這叫本征電子(洞)。

評論