欠采樣:基于SARADC的應用和技術

以低吞吐量運行SAR ADC可以實現多種優勢。通過增加轉換操作之間的時間,可以放寬系統濾波器要求,增加獲取輸入信號及從ADC抽取數據的時間。由于ADC的采集周期是轉換周期中讀取數據最常用的區域,因此,延長采集周期將放寬數字主機的要求。可以采用主機輸出-從機輸入(MOSI)時鐘速率較慢的低端處理器。例如,AD7980 16位SAR ADC的額定采樣速率最高為1 MSPS。

ADC的繁忙周期的最大額定值為710 ns,讀取數據的時間只剩下290 ns。要輸出16位數據要求時鐘周期不超過18 ns(或者不低于55 MHz左右)。然而,如果器件運行時的吞吐量為100 ksps,結果會使采集時間(數據讀取周期)從290 ns增至9290 ns。降低ADC采樣速率后,可以放寬串行時鐘要求,并把最小串行時鐘頻率改為2 MHz左右。在放寬數字主機要求以外,延長采集時間后,由于增加了建立時間,因此,還可以選擇使用低功耗和低帶寬ADC驅動器。

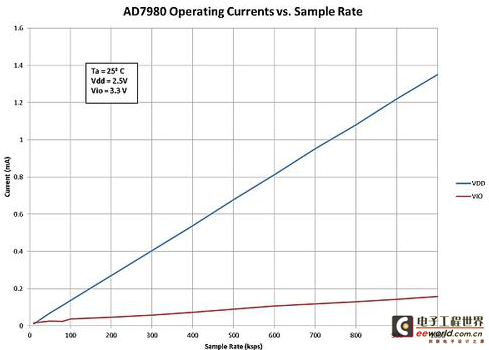

只要ADC支持需要的系統連續時間信號帶寬,就可以考慮使用額定最大吞吐量較低的ADC(如AD7988-1),以降低系統成本。AD7988-1是與AD7980同系列的一款100 ksps SAR ADC器件,它以較低的價格提供了相同的性能。如圖1所示,器件的功耗與采樣速率呈線性關系,因為多數功耗發生在活躍轉換周期中。減少轉換過程的次數,消耗的電量也會減少。速率為100 ksps時,AD7980(或AD7988-1)的功耗約為AD7980以1 MSPS的速率采樣時的十分之一。

圖1:AD7980工作電流與采樣速率

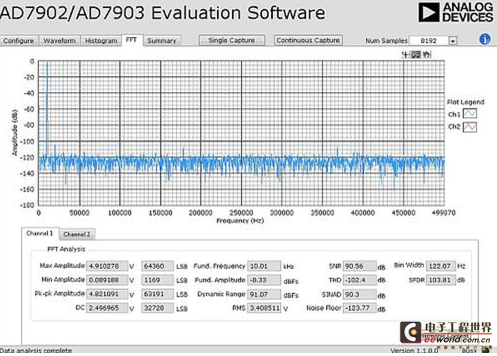

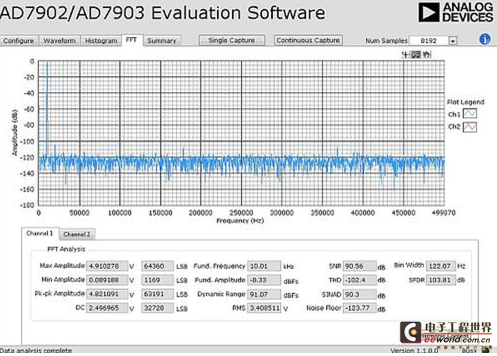

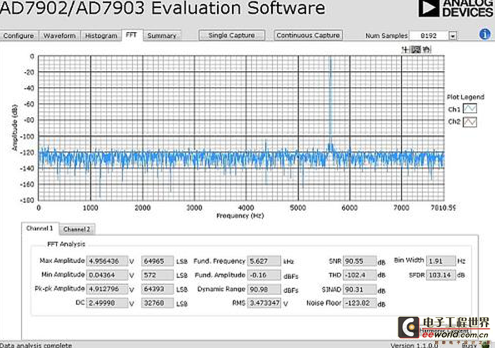

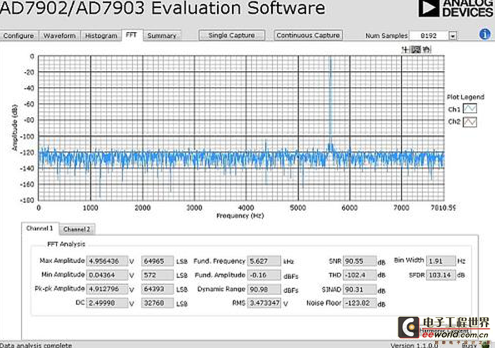

在單通道16位偽差分AD7980以外,ADI系列同時提供AD7902。這是一款雙通道16位偽差分同步采樣ADC,其額定采樣速率為1 MSPS。在傳播時間等應用中,可以利用同步采樣系統來抽取信號相位信息。我們收集了AD7902以1 MSPS和15.625 ksps(1 MSPS的1/64)的速率對10 kHz信號音采樣時的實驗室結果。運用等式4,欠采樣10 kHz信號音的基頻應該出現在DFT頻段中,該頻段跨度為5.625 kHz。可以看出,在符合奈奎斯特標準的采樣與欠采樣配置之間,無幅度信息丟失。但重構信號將為原始連續時間輸入的第一奈奎斯特區混疊表示。

圖2:AD7902的通道1(以1 MSPS對10 kHz信號音采樣)

圖3:AD7902的通道1(以15.625 KSPS對10 kHz信號音欠采樣)

欠采樣可能具有優勢的另一個例子是多通道順序采樣數據采集系統。這些系統一般由一個SAR ADC構成,帶有一個多路復用模擬前端,以固定間隔按已知順序轉換。在這種情況中,各個通道的有效采樣速率以系統中使能通道數的函數下降。例如,在一個八通道系統中,如果SAR ADC運行于1 MSPS下,則每隔八個樣本代表一個相應的通道。因此,給定通道的采樣速率僅為1 MSPS的1/8(125 ksps)。可以看到,在一個多路復用順序采樣系統中,單個通道的奈奎斯特頻率是如何快速降低的。

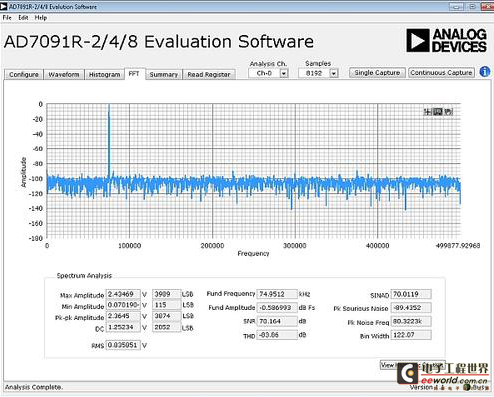

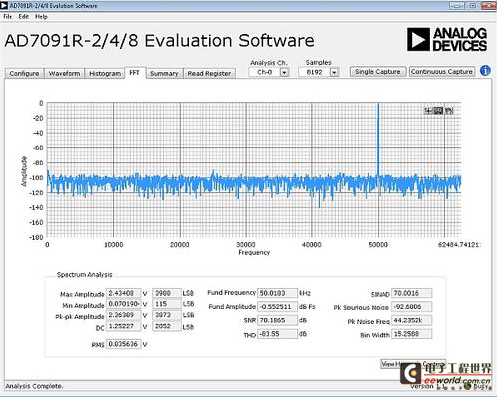

ADI公司提供AD7091R-8,這是一款超低功耗的12位、八通道1 MSPS SAR ADC,內置一個基準電壓源和一個用戶可編程的通道序列器。該器件采用4 mm x 4 mm LFCSP微型封裝,工作于3 V電源和1 MSPS采樣速率時,其功耗不高于1.7 mW。在AD7091R-8上,如果使能全部八個通道,器件就會按從通道0到通道7的順序,自動重復順序采樣。當ADC的采樣速率為1 MSPS時,每個通道將以125 ksps的速率采樣。因此,相對于1 MSPS單通道系統,給定通道的奈奎斯特頻率從500 kHz降低到62.5 kHz。在多路復用器的一個通道上監控75 kHz信號音,結果會產生連續時間信號的混疊表示,其基頻為50 kHz。如后續各圖所示,當通過使能AD7091R-8上的額外通道修正奈奎斯特標準時,動態性能并未下降。

圖4:AD7091R-8監控75 kHz信號音(僅使能一個通道)。

圖5:AD7091R-8監控75 kHz信號音(使能八個通道,通道采樣速率為125 ksps)。

本文闡述了這樣一種想法:在通信系統以外,有些應用可以用到欠采樣理論。這些應用可能包括RMS-DC轉換、交流應變計、傳播時間、超聲電平測量和多路復用采樣。用SAR ADC實現欠采樣系統可能帶來巨大的性能和功耗優勢。不但可以放寬系統的總體限制,同時還能實現電路的總體目標。

評論