保證嵌入式系統程序完整性的技術設計方案

2、安全性原則:由于設計中任何部件的安全性缺陷以及運行步驟上的漏洞都會導致系統被破壞的可能,所以本方案的安全性必須通過可信計算規范中可信鏈的建立過程進行論證。從而構造一個牢固的安全根基。

3、兼容性原則:基于嵌入式芯片廠商眾多,使用的架構也不盡相同。因此本嵌入式系統程序完整性保證設計方案應該盡量做到只經過有限的修改甚至無需進行修改,即可應用到大部分主流的嵌入式系統之中。保證本設計的通用性。

3 項目研制內容

本項目對嵌入式系統完整性保證技術中的加密算法實現,系統部件身份識別,系統運行效率等關鍵技術進行了綜合、深入的研究。

3.1 系統設計框架

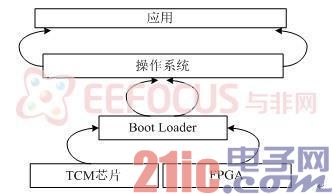

整個嵌入式系統設計總體結構圖如下圖所示,主要有主處理芯片、提供數據驗證功能的可編程邏輯器件(FPGA)、提供TCM規范服務的TCM芯片以及外部存儲器件。本系統運行與兩種模式下:1、主要由FPGA與PC進行數據交互的配置模式。2嵌入式處理芯片,FPGA,TCM芯片協同工作的運行模式。

配置模式下,FPGA讀出內部Device DNA,輸出到PC端。之后掃描外部存儲設備(如flash)制定地址區間的內容(一般為boot loader),進行SHA-1運算,產生數據摘要,輸出到PC端。Device DNA會作為DES算法的密鑰對上面提到的數據摘要進行加密,Device DNA與加密值會通過固件程序保存在TCM芯片的可信存儲區域內。

運行模式下,主處理芯片通過FPGA產生的時鐘信號進行工作。系統上電后,FPGA并不馬上對主處理芯片提供時鐘,而是先進行完整性驗證工作:1、裝載Device DNA,提供給內部DES運算部件作為密鑰使用。2、請求TCM芯片發送32位隨機數,此隨機數將會被DES算法加密后送到FPGA,FPGA的DES部件對其進行解密后,進行存儲。3、FPGA讀取flash制定區域的內容,并進行SHA-1運算,產生160位數據摘要。4、160位數據摘要被分為5組,每組32位。每組與此前接收到的32位隨機數組成64位數據,進行DES加密后,送到TCM芯片進行校驗。5、TCM芯片接收到5組數據后進行解密。首先校驗隨機數部分是否與之前發出的一致,若一致,則繼續校驗數據摘要部分數據與之前在配置模式下寫入的理想值是否一致。對比結果存放于特定內存位置。6、FPGA為主處理芯片提供時鐘,并接通主處理芯片與外部存儲器與TCM的數據通路。用戶可以通過相關的接口讀取對比值,判斷系統是否被修改。

嵌入式完整性保證方案框架

3.2 安全性分析

硬件安全性: Spartan-3A,全部硬件邏輯固化在芯片內部,不可讀取。TCM:通過國家商密辦檢驗,不可讀取。Boot Loader完整性:FPGA將依次讀取Boot Loader的內容,并計算Hash值。對Boot ROM的任何篡改都將改變Hash值。從而導致驗證不通過。

以下是幾種可預見的攻擊方式:1、在已知Boot loader的內容的前提下,計算出數據摘要的內容,偽造FPGA。由于Device DNA是每一塊FPGA的身份識別碼,此值是唯一的。更換FPGA會導致用于DES加密密鑰的Device DNA改變,從而向TCM芯片傳送的加密值不正確。2、監聽FPGA與TCM之間的通訊。由于TCM與FPGA通訊內容還依賴于隨機數,具有不可預見性,所以監聽當次的通訊內容對之后內容的破解并沒有作用。

3.3 可信鏈的建立

如之前所提到,一個可信的系統的建立,必須是硬件,操作系統,軟件應用三者共同作用的結果,本完整性保證設計也不例外。本次設計的可信根建立于以下兩個事實之上:1、TCM的保密區域存儲空間不能被讀取。2、FPGA的Device DNA是唯一對應于一塊FPGA的。

經過3.1小結的驗證步驟,我們把可信根擴展到了Boot Loader。Boot Loader是嵌入式系統中用于系統初始化以及載入操作系統的程序。保證Boot Loader的完整性的意義在于保證了操作系統在正確的環境以及以正確的方式被加載。之后程序員就可以通過軟件的手段對建立在操作系統之上的應用進行安全保證。

信任鏈的建立及傳遞

5 研制成果及應用

5.1 研制成果

本項目的主要研制成果有三個方面:

完成了一套具備可信計算功能的硬件開發板。

經過了一年的研發,本開發板的各項功能都被驗證具備穩定運作的能力,由于其采用的是主流的資源配置,因此可擴展性也是有目共睹的,具體指標如下:

ARM7內核的三星44B0X處理器,最高運行速度達到66Mhz

Xilinx Spartan3A FPGA芯片,多達200萬門的可編程邏輯資源

16M Nor Flash,16M SDRAM能滿足大部分應用需要

100M網絡接口,支持高速內核下載及燒寫

2個標準UART-232接口,能提供與TCM芯片的穩定連接及常見外設的數據傳輸

完成了TCM固件程序開發及uclinux工具鏈的配套

目前,我們已經利用中興提供的開發平臺開發了相關的TCM固件程序,使得TCM芯片與本嵌入式平臺在啟動階段可以自動完成驗證功能。而與此同時,通過進一步的固件程序開發,TCM芯片可以提供更豐富的驗證加密功能,以滿足更多的可信計算需要。

與此同時,通過busybox工具鏈,也成功把uclinux2.4成功移植到本嵌入式平臺上,運行正常。

6 項目總結

通過本項目的研發,項目組總結經驗如下:

1) 需要注意項目經驗的積累及轉化。從2008年12月提出設計方案到2010年產品的實現,其中進行過數次的方案改動。改進方案的建議不僅來自領隊老師自己,還來自參與本項目的學生和過程中不斷吸收進來的一些最新的外來研究經驗和成果。不斷的改進并不代表對之前工作的否定,恰恰相反,沒有一些針對前期方案的準備和工作的體會,是沒有可能提出更成熟,更穩定的改進方案。因此,在項目實施過程中,積極與外界溝通,同時組織團隊進行方案的再三討論,對于項目的實施和進步是十分有利的。

2) 對中間結果進行規范化的制作,形成可用的產品。在本項目進行的過程中,恰逢IBM PowerPC與工業和信息化部IP核標準工作組共同推廣中國開源IP標準化工作。于是在保證工作質量和進度的前提下,我們嘗試把嵌入式系統程序完整性保證的概念移植到PowerPC支持的PLB總線上。同時參照相關的標準化要求,完成了“帶有完整性驗證功能的外部存儲控制器”的IP核標準化設計。最終在這個過程中,不僅使學生的能力得到鍛煉,同時還驗證了本設計的可擴展性和可移植性。

評論