EP1C6Q在水輪機組轉速測量中的應用

關鍵詞:狀態監測;現場總線;現場可編程門陣列;EP1C6Q

隨著工業生產與科學技術的發展,大型水輪機組的自動化水平也在不斷提高。而這些設備一旦發生故障,將會給人們的生活和生命財產造成極大的威脅。因此,對其運行狀態進行監測,及時發現故障征兆具有重要意義。現場可編程門陣列(FPGA,Field Programmable Gate Array )的出現是超大規模集成電路和計算機輔助設計技術發展的結果。它具有集成度高、多功能、低功耗、開發周期短等特點,而且可以很方便地對設計進行在線修改,因此獲得了廣大用戶的青睞,應用范圍也越來越廣。本文首先介紹了ALTERA公司推出的低價位、高性能CYCLONE系列FPGA器件EP1C6Q的特點和內部結構,然后結合在水輪機組狀態監測開發系統中遇到的實際問題,給出了相應的解決方案,最后就開發過程中遇到的一些實際問題,提出了筆者自己的看法。

1 EP1C6Q的結構特點

EP1C6Q是ALTERA公司低價位CYCLONE系列FPGA的一種。它采用1.5V內核電壓,內嵌92106位存儲區間,可提供兩個鎖相環和雙倍數據傳輸速率(DDR)的接口電路。其具體特點如下:

●采用240個引腳的FPQF封裝形式,能提供185個IO用戶引腳和5980個邏輯單元。

●具有20個4608位的RAM存儲區,最高可支持200MHz的數據傳輸。每個存儲區均包括單口或雙口RAM、ROM、FIFO等各類存儲器件,并支持8位、16位、32位、36位等數據存儲類型。

●片上的鎖相環電路可以提供輸入時鐘的1~32分頻或倍頻、156~417ps移相或可變占空比的時鐘輸出,輸出時鐘信號的特性可直接在開發軟件QUARTUS2里設定。經過鎖相環輸出的時鐘信號既可以作為內部的全局時鐘,也可以輸出到片外供其它電路使用。

●多功能的IO結構支持差分和單端輸入,并與3.3V、32位、66MHz的PCI局部總線兼容;IO輸出可以根據需要調整驅動能力,并具有壓擺率控制、三態緩沖、總線狀態保持等功能;整個器件的IO引腳分為四個區,每一個區可以獨立采用不同的輸入電壓,并可提供不同電壓等級的IO輸出。

水輪機組的工作效率是系統狀態監測中的一項重要指標,而機組的工作效率與當前時刻的轉速密切相關。轉速測量的關鍵是對六十五路脈沖信號周期的測量。筆者采用了EP1C6Q器件內部的65個計數器同時工作的測量方法。

2.1 水輪機組轉速測量原理

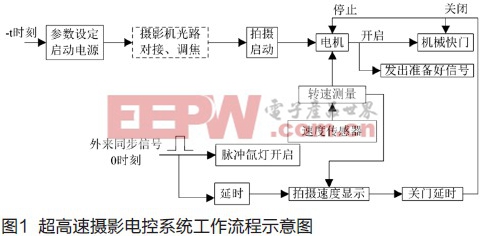

該水輪機組轉速測量裝置如圖1所示,它由六十五個微型機械傳感器組成,其中六十四個傳感器分布在對稱的四個轉軸上,第六十五個傳感器在軸的中心交點。流經管道的水流將帶動傳感器的旋轉。當傳感器旋轉一周后,觸發電子線路產生一個脈沖信號。管道中水流的速度越快,脈沖信號的間隔越短;管道中水流的速度越慢,脈沖信號的間隔越長。這樣?就可以根據脈沖信號的間隔或者說兩個信號上升沿的時間長短來計算流速的大小,從而依據相應的公式計算水輪機組轉速的大小。

2.2 整體設計方案及工作原理

該水輪機組系統設計方案的整體框圖如圖2所示。水輪機組狀態監測系統采用LonWorks現場總線技術,神經元芯片是構成系統采集節點的核心,它內部包括三個微處理器,即MAC處理器、網絡處理器、應用處理器,而11個輸入/輸出引腳則可根據不同的外部設備來靈活配置。收發器是節點之間通信的橋梁。

由于水輪機組轉速比較慢,傳感器發出的脈沖信號的時間間隔較長?因此?對緩變信號周期的測量應采用測周的辦法。首先是將輸入的脈沖信號經去抖、限幅后變成符合EP1C6Q輸入信號特性要求的信號,然后當EP1C6Q接到神經元信號的測量命令后,再捕捉輸入信號的上升沿。為了保證所有的通道在神經元芯片讀取數據之前已經鎖存,讀取數據的時間間隔應保證不小于兩個信號周期。神經元芯片將每個通道的計數值存儲到片內RAM區,并將計算得到的轉速值送到信號處理模塊,以計算水輪機組的工作效率。由于流速測量傳感器的分布特點是邊緣傳感器的信號周期比內部傳感器的信號周期長,因此,筆者選擇一個最靠邊的傳感器作為標志傳感器,并由標志傳感器產生讀取數據的標志位信號。

2.3 硬件實現

(1) 信號調理電路

由于EP1C6Q輸入/輸出邏輯高電平僅能支持4.1V,而不能直接與標準的TTL電平信號相連,因此,神經元芯片和EP1C6Q之間的連接以及脈沖輸入電路都必須加限幅電路。芯片的設計已經考慮到與5V設備的連接問題,其解決方法是在連接線路中串接一個162Ω電阻。

(2) EP1C6Q和神經元間的物理連接

在轉速測量模塊中,EP1C6Q主要起信號邊沿檢測、脈寬測量以及實現神經元芯片外圍邏輯電路的作用。由于許多功能是在EP1C6Q內部利用軟件實現的,所以二者之間的連接很簡單。控制信息的傳遞主要有兩個途徑:一是通過神經元芯片的I/O引腳,由于I/O引腳較長的建立時間會影響系統的實時性,因此,設計電路僅使用IO0、IO1兩個通道來作為整個系統的異步清零(clr)和讀取數據標志(read_time);另外一個途徑是通過神經元芯片的數據總線(D0~D7)和地址總線?A0~A15?,即在EP1C6Q的內部設立狀態寄存器,并由神經元芯片向寄存器中寫入不同的數據,然后由寄存器根據寫入的數據來使相應的控制信號有效。

2.4 軟件設計

a.EP1C6Q內部程序

EP1C6Q的內部程序是在QUARTUS2開發軟件中實現的。QUARTUS2能夠支持原理圖輸入和硬件描述語言兩種編程方式。整個程序包括譯碼電路、分頻電路、計數控制電路、計數器模塊和數據的鎖存和讀取等五個部分。具體如下:

(1)計數控制電路

EP1C6Q內部的程序是在神經元芯片的控制下運行的。其控制部分電路如圖3所示。信號fin代表六十五路脈沖輸入信號的一路,clk0代表標準的計數時鐘。在clr信號由低電平變為高電平、且start置為高電平后,脈沖信號fin輸入有效。當第一個上升沿到來后,計數器的PUL引腳變為高電平,此時,計數器開始計數;當第二個上升沿到來后,PUL變為低電平,計數器停止計數;而當第三個上升沿到來后,read_time信號變高電平,數據鎖存。

(2)計數器的設計

由于水輪機組的轉速比較慢,產生的脈沖信號頻率一般在0.01Hz~10Hz之間,因此,轉速快和轉速慢時的信號周期差別比較大。為滿足1/10000個計數時鐘的精度要求,計數器的計數位數應設計為20位。計數器的最大設定值為1000000,這樣,當脈沖信號周期在10Hz~0.1Hz之間時,計數時鐘為100kHz;而當脈沖信號的周期在0.1Hz~0.01Hz之間時,計數時鐘自動轉換為10kHz。計數時鐘的自動切換是由計數器的溢出標志控制的,當計數器的計數值超出設定的最大值(1000000)后,溢出標志由低電平變為高電平,這樣,經過全局時鐘分頻計數的時鐘分頻次數也會相應地擴大10倍,從而保證了計數器不會再次溢出。

(3)狀態寄存器設計

為了減小神經元芯片控制功能對IO引腳的依賴,EP1C6Q在其內部設立了兩個狀態寄存器。這兩個狀態寄存器可根據神經元芯片寫入的控制字來使相應的控制信號有效。使用的控制信號如下:

start:通過神經元芯片要求EP1C6Q進入信號采集狀態控制,高電平有效。

lck:數據鎖存信號,低電平有效。當EP1C6Q的輸出信號read_time有效后,神經元芯片向狀態寄存器寫入命令字以使lck信號有效。為了保證所有通道的計數器已經停止工作,神經元芯片接收到read_time后將延遲ΔT時間后再鎖存計數器的數據。

h1?h2:計數值高八位、中八位、低八位的選擇控制。為了滿足系統要求的測量精度, EP1C6Q內部采用二十位計數器對每一路信號進行計數,而神經元芯片的數據總線是八位,因此需要分三次讀出。

(4)譯碼電路設計

神經元芯片一般采用內存映象法進行數據的傳遞。所謂內存映象法,是指給芯片外部的寄存器、存儲器或IO單元分配一個物理地址,以便于對外設操作,這相當于對該物理地址的操作。譯碼電路主要提供FLASH、狀態寄存器和六十五個計數器的片選信號。系統的地址分配如下:

E800~EFFF?數據存儲區,用于保存各個通道的計數值。

0000~7FFF?外圍FLASH區。

8000~8040?六十五個計數器的內存地址。

8041~8042?狀態寄存器的內存地址。

8042~E7FF?用戶備用空間。

(5)分頻電路

計數器單元的計數時鐘是把輸入的全局時鐘分頻得到的。12MHz的有源晶振輸出通常可作為全局時鐘,分頻電路采用VHDL語言設計,分頻次數設定值的變換由計數器的溢出標志控制。

b.神經元芯片的內部編程

本編程設計主要用于完成與系統的同步和控制EP1C6Q程序的運轉。當接到信號處理模塊發來的數據請求信號后,該程序將啟動EP1C6Q內部程序并開始計數,以將最終的計數值讀到內部RAM區。

3 注意事項

在整個設計方案的實現過程中,應仔細考慮以下兩點:

第一是芯片的選擇。與普通電路開發不同的是,本設計方案的前期編譯和仿真驗證不需要拘泥于某一具體型號的芯片,只要滿足方案所需的邏輯單元的數量、控制時序的精度和存儲區間的大小等要求,就可以在軟件開發工具中編譯仿真。可到方案成熟后,再考慮一些細節問題,如芯片以及所需電源和配置芯片是否容易買到,提供的IO接口類型是否滿足需要,芯片的封裝形式是否會影響到PCB板的制作等問題。

第二是時序電路和組合電路的轉化。在一個系統中,時序電路和組合邏輯電路一般同時存在。兩種類型的電路都作為輸入時,為避免毛刺現象,可以在組合邏輯的輸入之前加D觸發器,以將組合邏輯電路轉化為時序電路。在多級時鐘系統中,為了滿足建立和保持時間的要求,往往需要在低頻時鐘信號驅動的邏輯電路的輸出端加一級高頻時鐘信號驅動的D觸發器,以實現時鐘之間的同步。但這樣做會增加輸入和輸出之間的時間延遲,嚴重時可能通不過編譯軟件的時序驗證。因此,可以將其轉化為簡單的組合邏輯電路,以使其比較容易實現。

4 結束語

該方案已經通過了實驗驗證,測量結果能夠滿足設計要求。考慮到成本問題,選擇的芯片不能與5V系統直接相連,這使得多路輸入信號給整個電路的設計帶來了一定的困難。如果排除這些因素,該方案還可以得到進一步的改善。

評論