基于89C56的智能探測器的設計與實現

摘要: 針對高精度穩壓電源的需求情況,本文提出了一種用于噪聲電壓檢測的探測器設計方案,文章詳細介紹了該探測器總體設計方案以及核心組成模塊。系統的核心模塊為高速微控制器89C56,文中詳細介紹該芯片的特點和檢測原理。并且設計中實現了一個分析和預測模塊,使得該探測器成為一個智能探測器。

關鍵詞:噪聲檢測;智能;探測器;微控制器;89C56

1 前言

近年來,隨著計算機、微電子、通信及網絡技術的發展,人們對設備的可靠性、體積、功耗等方面提出了越來越高需求,尤其是在一些尖端領域,對設備的各種參數指標都提出了嚴格要求。在某大型設備的研制過程中,按設計要求,需要高精度穩定電壓,如果電壓不穩定或者有噪聲信號,需要提供預警措施,因此在設計中除了需要對穩壓電源進行很好地設計,提供良好、完善的濾波去噪功能,還需要設計一個專用的噪聲探測模塊,針對該需求,本文提出了一種基于高性能微控制器的智能噪聲電壓探測器的設計與實現方案。

在硬件上,智能探測系統以微控制器為核心,以各種常用組成部件的并集為基本要素,構建的硬件設計和探測系統。

2 智能探測器總體設計方案

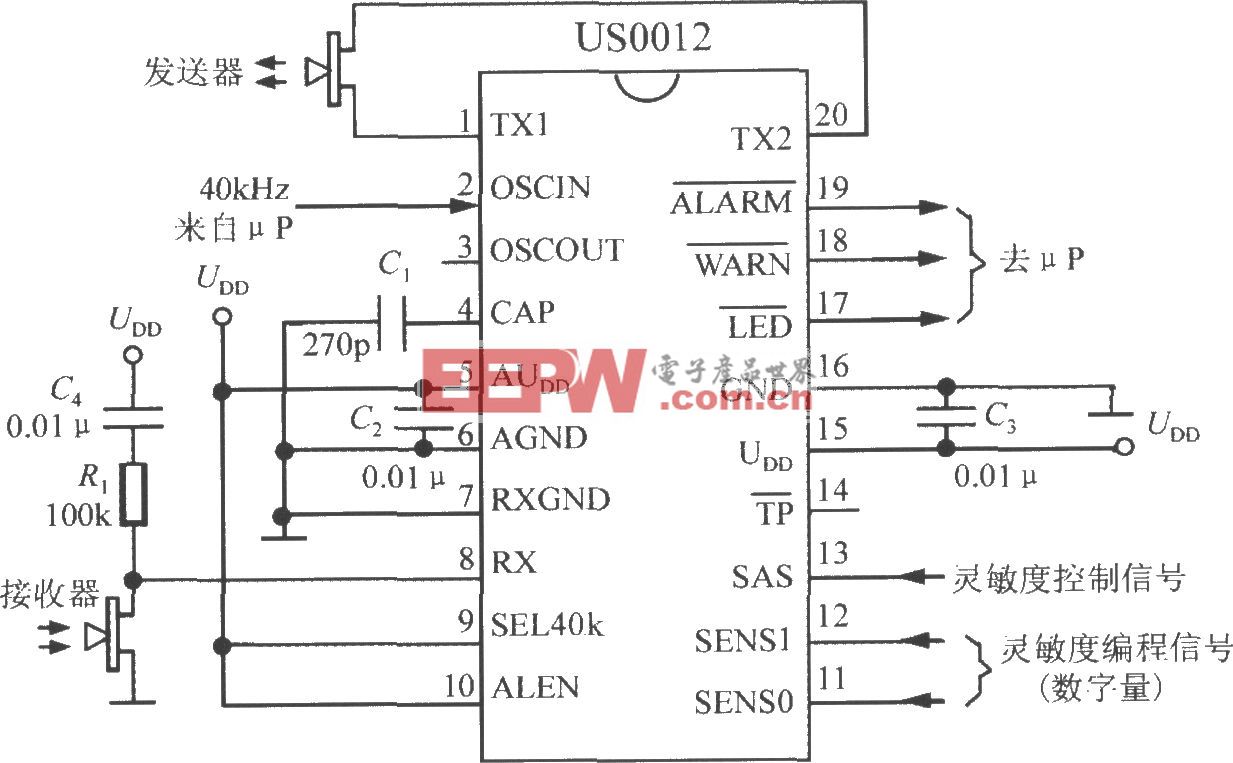

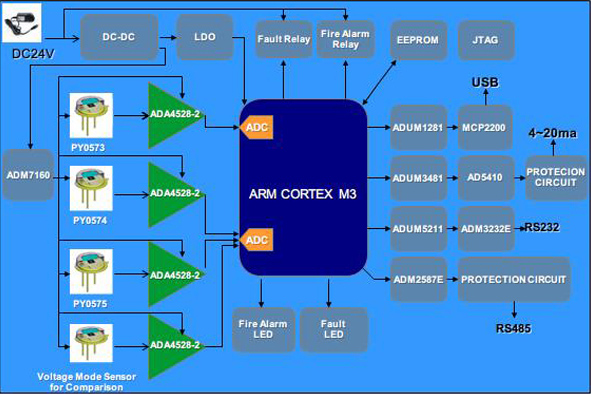

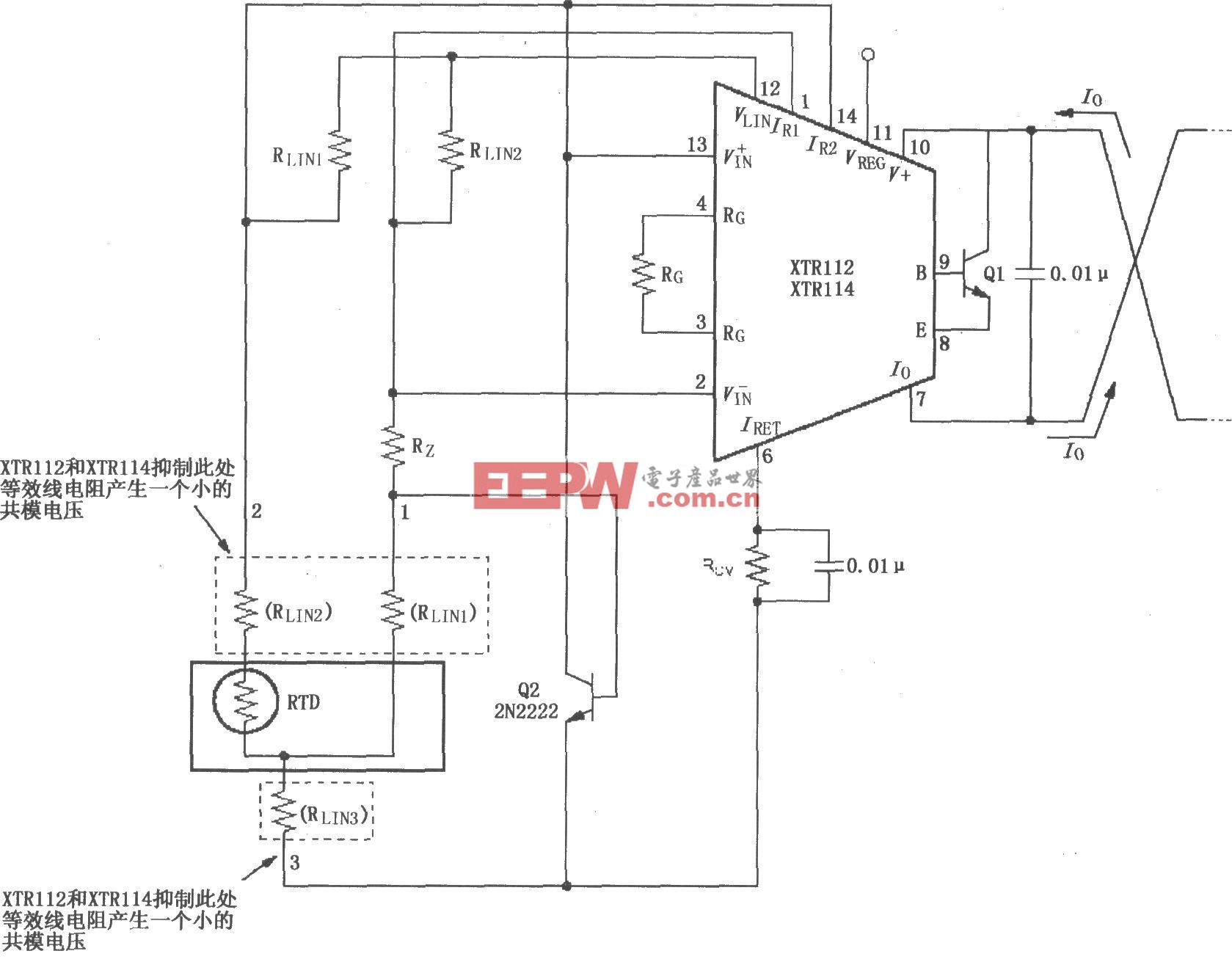

智能探測器是以高速微控制器89C56為核心,擴展了存儲器、信號采集模塊、電壓比較器、電源電路等模塊,組成了一個板級的基本系統,其邏輯結構如圖1所示。

圖 一:智能探測器總體結構圖

探測器首先通過信號采集模塊,從探測目標系統中獲取電壓信號,然后經過電壓比較模塊,將獲得的電壓信號與預先設定的電壓值進行比較,判斷當前獲取的電壓信號中是否有噪聲,噪聲值準確的又是多少。如果噪聲值超出一定范圍,此時通過A/D轉換模塊,將信號由模擬的轉換成數字信號,并交給核心處理器進行處理。

在實際電路中,DAC使用的是微控制器C8051F020片內集成的12位轉換器。片內的DAC輸出擺幅均為0V 到VREF-1LSB,對應的輸入碼范圍是0x000 到0xFFF,可以用相應的控制寄存器允許或禁止。在被禁止時DAC的輸出保持在高阻狀態,供電電流降到1µA或更小。它具有靈活的輸出更新機制,允許無縫的滿度變化并支持無抖動輸出更新。在缺省方式下,DAC的輸出在寫DAC 數據寄存器高字節(DACxH)時更新。寫DACxL時數據被保持,對DAC輸出沒有影響,直到對DACxH的寫操作發生。如果向DAC數據寄存器寫入一個12位字,則這個12位的數據字被寫到低字節(DACxL)和高字節(DACxH)數據寄存器。在寫DACxH寄存器后數據被鎖存到DAC。DAC可以被用于8位方式,這種情況是將DACxL初始化一個所希望的數值(通常為0x00),將數據只寫入DACxH。DAC的輸出更新也可以由定時器溢出事件觸發。在這種更新方式下,對DAC 數據寄存器的寫操作被保持,直到相應的定時器溢出事件(分別為定時器3 定時器4 或定時器2 )發生時DACxH:DACxL的內容才被復制到DAC 輸入鎖存器,從而允許DAC 數據改變為新值。

為了確保探測器足夠高的靈敏度和響應速度,系統采用了高速微控制器89C56,其最高頻率可達1MHZ,能夠在探測目標發生變化1us后做出反應。同時利用微控制器中強大的運算性能,能夠存儲之前發生的一定狀態,并對當前狀態進行預測,使得該探測器具有一定智能。

3 89C56高性能微控制器

系統的核心處理器采用是MicroChip的高速微控制器89C56。該芯片采用高速、流水線結構的8051兼容的CIP-51內核,具有32個I/O引腳;片內集成多種標準外設接口、PGA、模擬多路開關、DAC和ADC等等,可以最大限度的減少外設的數量和PCB電路板大小;片內具有64K字節可在系統編程的FLASH存儲器,支持全速、非侵入的在系統調試。它具有以下主要特性:

l 高速、流水線結構的8051兼容的CIP-51內核,可達1MIPS;

l 全速、非侵入式的在系統調試接口(片內);

l 真正12 位,100 ksps 的8 通道ADC,帶PGA和模擬多路開關;

l 兩個12位DAC,可編程更新時序;

l 64K字節可在系統編程的FLASH存儲器;

l 4352(4096+256)字節的片內RAM;

l 可尋址32K字節地址空間的外部數據存儲器接口;

l 硬件實現的SPI、SMBus/ I2C和兩個UART串行接口;

l 5個通用的16位定時器;

l 具有5個捕捉/比較模塊的可編程計數器/定時器陣列;

l 片內看門狗定時器、VDD監視器和溫度傳感器。

具有片內VDD監視器、看門狗定時器和時鐘振蕩器的89C56是真正能獨立工作的片上系統。所有模擬和數字外設均可由用戶固件配置為使能或禁止。每個MCU 都可在工業溫度范圍(45℃到85℃)內用2.7V~3.6V 的電壓工作。所有的端口I/O、|RST和JTAG引腳都容許5V的輸入信號電壓。

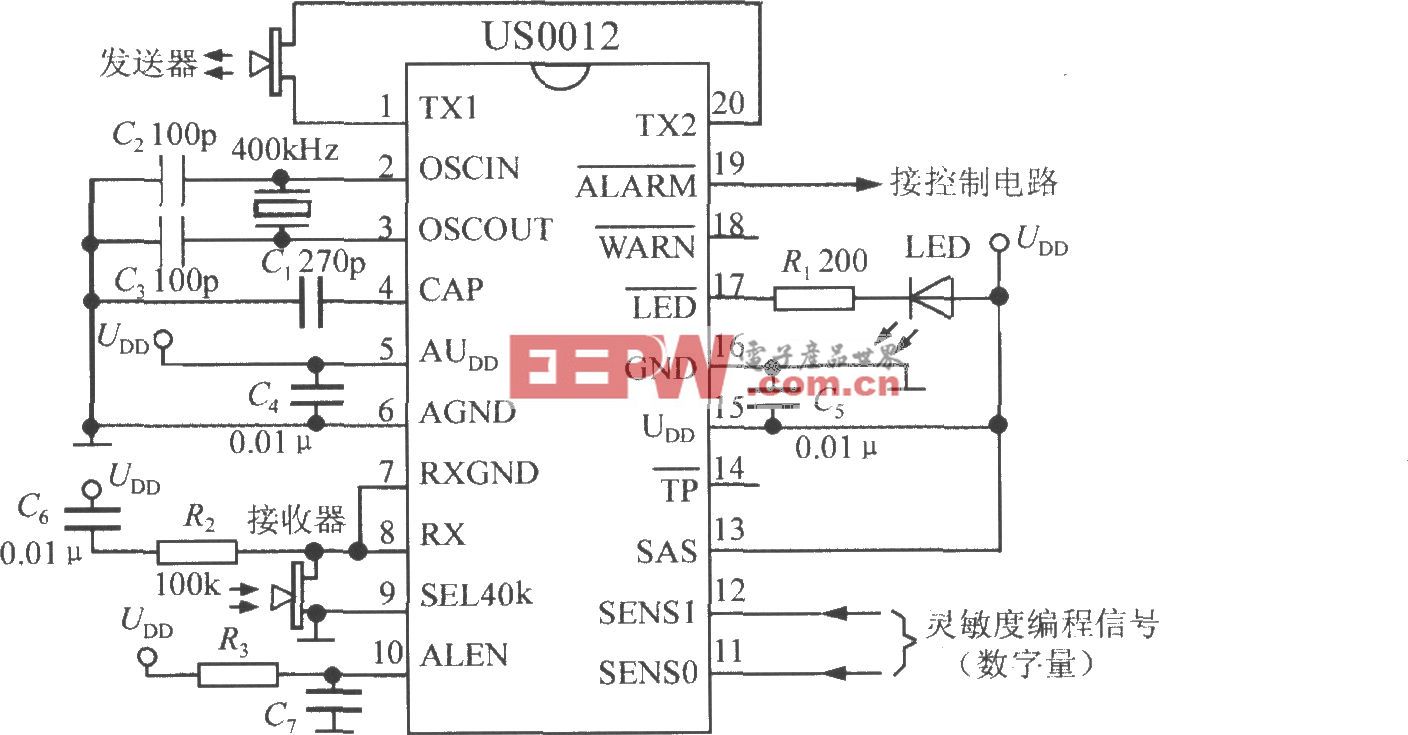

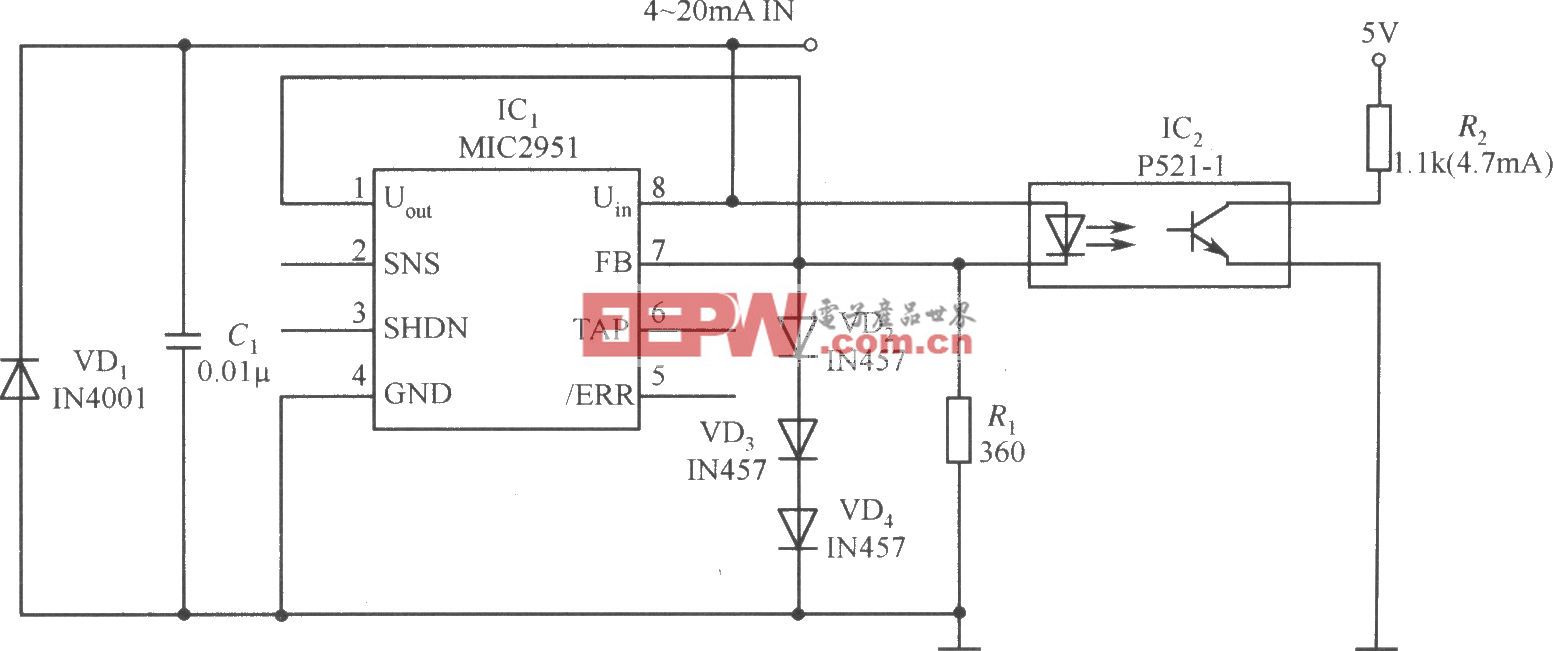

89C56集成有JTAG調試電路,片內FLASH存儲器具有在系統重新編程能力,可用于非易失性數據存儲,并允許現場更新8051 固件。解析儀根據該芯片所具有的這些特性,在硬件設計中增加了JTAG接口電路。這樣一來,解析儀便可以通過專用JTAG適配器與微機相連,使用Cygnal集成開發環境對89C56 MCU進行非侵入式(不占用片內資源)、全速、在系統調試。該調試系統支持觀察和修改存儲器和寄存器,支持斷點、觀察點、單步及運行和停機命令。在使用JTAG 調試時,所有的模擬和數字外設都可全功能運行。另外,利用JTAG接口和片內FLASH存儲器的在系統編程能力,可以方便地實現固件升級。89C56內部結構圖如圖二。

圖 二: 89C56內部結構圖

4 智能預測模塊

系統除了能實時地檢測被測系統的噪聲狀態外,還能夠根據之前遇到的噪聲情況,對當前出現的噪聲信號預測其后是否還會出現更多、更大的噪聲信號。其預測原理是每次發現又較大噪聲信號到來時,通過高速微控制器采集和處理這些噪聲信號,并將其噪聲的幅值、持續的時間存儲在微控制器外圍的存儲器中。一旦下次再檢測到一個新的噪聲信號時,首先將此噪聲信號采集并送入微控制器中,然后微控制器根據該噪聲的幅值和已經持續的時間與庫里面存在的噪聲信號進行對比,設定一個閾值,如果對比的差額小于該閾值,則從所有小于該閾值的數據中找出與之最接近的歷史噪聲數據,并將此歷史噪聲數據做上標記(記錄已經匹配的次數),此時系統認為遇到了很可能是之前重復出現過的噪聲信號,于是給系統發出報警信息,并繼續監控新到來的噪聲信號,可根據預先設定的匹配程度(閾值),做出當前的噪聲信號是否為真正的重復噪聲的最終判斷。如果經對比,發現庫中所有的數據與之對比后差值都超出了該閾值,則認為當前檢測的噪聲信號是一種新的噪聲信號,并將其存儲到外部存儲器中。如果外部存儲器已經存儲滿了,則找一個標記最小的數據,進行覆蓋(即覆蓋掉的數據是重復出現幾率最小的噪聲信號,此類信號對噪聲的預測幫組不大)。按此策略設計后,可使得該檢測系統能夠對當前遇到的噪聲信號做出一定的預測和報警功能,以便總體設計者根據該探測器分析和定位噪聲產生的原因和時機,為最終消除該噪聲信號提供有效的參考信息。其中存儲噪聲信息的數據格式如圖三所示。

圖 三: 存儲噪聲信息的數據格式

5 創新點總結

本文的創新點在于將高速微控制器與A/D轉換器等器件有機結合起來,開發了一個適用于精密穩壓電源的智能檢測系統,該系統除了具有靈敏的檢測噪聲信號的功能,還能根據歷史出現過的噪聲信號做出預測和判斷,給設計者提供預警信息。通過該探測器的設計與實現為設計者提供有效的精密、純凈電壓有很大的輔助作用,此外該系統也能應用與其它一些電壓檢測環境。

參考文獻:

1 王承何志偉基于虛擬儀器的網絡化自動測試系統的構架及實現電子技術應用 2002

2 陳永泰 劉雪燕 AD9852與AT89C51在信號源中的應用中國電子元器件,2002

3 邵貝貝,劉慧銀編著. 微控制器原理與開發技術. 北京:清華大學出版社,1997

4 馬鳴錦,趙秋霞,曾光裕. 高性能個人計算機硬件結構及接口. 國防工業出版社,2001

5 何立民 . 單片機高級教程-應用與設計 . 北京航空航天大學出版社

6 張景春;侯國強;唐瑞尹;孫艷彬 單片機測控技術在平板導熱系數儀研制中的應用,北京,《微機算計信息》,2005.No.5,P173

評論