基于FPGA設計EnDat編碼器數據采集后續電路

1.3 時序和OEM數據存儲

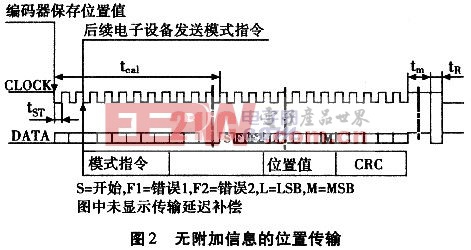

在每一幀同步數據傳輸時一個數據包被發送,傳輸循環從時鐘的第一個下降沿開始測量值被保存,計算位置值。在兩個時鐘脈沖(2T)后,后續電子設備發送模式指令“編碼器傳輸位置值”(帶或不帶附加信息)。在計算出了絕對位置值后(見圖2),從起始位開始編碼器向后續電子設備傳輸數據,后續的錯誤位F1和F2(只存在于EnDa2.2指令中)是為所有的監控功能和故障監控服務的群組信號,他們的生成相互獨立,用來表示可能導致不正確位置信息的編碼器故障。導致故障的確切原因保存在“運行狀態”存儲區,可以被后續電子設備查詢。

從最低位開始,絕對位置值被傳輸,數據的長度由使用的編碼器類型決定。傳輸位置值所需的時鐘脈沖數保存在編碼器制造商的參數中。位置值數據的傳輸以循環冗余檢測碼結束。

位置值如果帶附加信息,緊接在位置值后的是附加信息1和2,他們也各以一個CRC結束(見圖3)。附加信息的內容由存儲區的選擇地址決定,然后在后面的采樣周期里被傳輸。在后續的傳輸中一直傳輸該信息,直到新的存儲區被選擇。在數據字的結尾,時鐘信號必須置高電平。10~30μs或1.25~3.75μs(EnDat可編程的恢復時間tm)后,數據線回到低電平,然后,新的數據傳輸可在新的時鐘信號下開始。

同時,編碼器為參數提供了不同的存儲區,它們可以被后續電子設備讀取,這些區域可以被編碼器制造商、OEM廠商甚至最終用戶寫入。一些特定的區域是可以被寫保護的。不同系列的編碼器支持不同的OEM存儲區和不同的地址范圍。因此,每一個編碼器必須讀取OEM存儲區的分配信息。基于此原因,后續電子電路應基于相對地址編程,而不能使用絕對地址。

2 EnDat接口后續電子設備的電路設計方案

全數字化交流伺服系統中采用TMS320F2812作為控制器,用以實現位置環、速度環和電流環以及SVPWM、電壓和電流采樣等功能。此外,采用Altera公司的型號為EPlC6Q240C8的Cyclone系列FPGA實現與編碼器接口、譯碼邏輯等功能。同時,在FPGA內部實現了128B的雙口RAM,通過總線實現與DSP之間的數據傳輸,功能框圖如圖4所示。

評論