圖像采集壓縮和高清分析并行處理的硬件系統設計

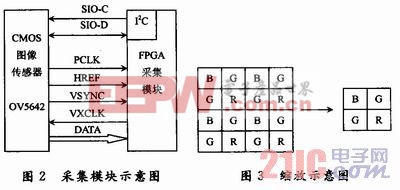

通過SCCB總線設置OV5642相關的內部控制寄存器,實現對OV5642初始化,從而確定輸出分辨率、開窗位置、曝光時間等。SCCB總線是Omni Vision公司特有的一種三線串行攝像控制總線。三線中的SCCB_E為片選信號線,本文中只有OV5642一個從設備,所以SCCB_E直接置低,始終選中OV5642。在模擬I2C控制器控制下,第一步,SIO_D線傳輸OV5642的器件地址加上寫操作標識,確定操作的器件和注明是寫操作;第二步,傳輸內部的目標寄存器的地址;第三步,傳輸要設置的數據并寫入到對應的寄存器中,完成寄存器配置。

采集控制器是在FPGA設置的一個時序邏輯控制器,主要產生OV5642需要的外部時鐘XVCLK和根據OV5642輸出的像素時鐘PCLK,行參考時鐘 HREF,幀同步時鐘VSYNC產生讀寫控制存儲信號。通過對PCLK,HREF,VSYNC時鐘的計數,可以得到寫滿一行或者一幀信號,為后繼處理提供同步時鐘和使能信號。

2.2 預處理模塊設計

預處理模塊主要是利用FPGA可編程性和內部豐富的硬件資源,在硬件層面選擇性的傳輸數據,將高清圖像的分辨率降低。FPGA采集到的原始圖像數據格式為Bayer RGB格式,每個像素點只有一種顏色分量,其余顏色分量可以通過插值算法恢復。如圖3左邊所示就是4×4的Bayer RGB格式。為了保持數據格式一致性,需要每隔2行或者每隔2列選擇一個像素傳輸。本設計采用在行方向上每隔2列選擇傳輸一個像素點,在列方向上每隔2行選擇傳輸一個像素點。這樣能將圖像分辨率降低,達到縮放目的,如圖3所示。

圖像數據是逐個像素逐行串行傳輸的,在縮放處理上,利用PCLK,HREF和VSYNC信號時序關系產生計數脈沖和使能信號。在行方向上,選擇傳輸一個像素點數據后,利用PCLK作為列計數脈沖,每過兩個脈沖(隔兩個像素點)再選擇傳輸一個像素點數據,一直循環選擇,直到處理完一行圖像數據。這時根據 HREF信號產生列計數器清零信號,將列計數器清零,暫停數據選通。在列方向上,由行計數器利用HREF信號進行計數,每過兩個計數脈沖(隔兩行圖像數據),重復行方向上的處理方式對當前行進行選擇數據傳輸。如此循環處理,直到一幀圖像數據處理完畢。每幀圖像處理完畢信號是由VSYNC信號產生的。同時,VSYNC信號對行計數和列計數器清零,直到新一幀圖像到達,計數器重新計數,開始新的一幀圖像縮放處理。通過這樣的縮放處理,可以將2 592×1 944的圖像降為648×486的圖像,數據量得到減少。預處理模塊將縮放后圖像傳輸到DSP中處理。

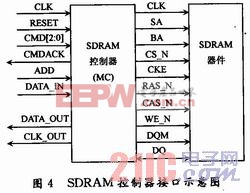

2.3 SDRAM控制器(MC)的設計

SDRAM控制器模塊是FPGA內部設計的模塊,用于將圖像數據傳輸到外部存儲器暫存。圖4為FPGA設計的頂層模塊示意圖。在MC控制器的內部,采用狀態機來實現數據讀寫、設置模式寄存器和刷新等操作的命令譯碼,產生輸出給SDRlAM芯片的RAS/CAS/WE/CS/DQM等信號。已經初始化的SDRAM在得到了RAS,CAS,WE的值后開始執行相應的命令。在對SDRAM進行讀、寫操作過程中,要先進行頁激活操作,保證存儲單元是打開的,再通過預充電命令實現來關閉存儲單元。在進行寫操作時,內部的列地址和數據都會被寄存,而進行讀操作時,內部地址被寄存,數據的讀取則發生在CAS延遲時間(通常為1~3個時鐘周期)后。SDRAM順次的進行讀、寫操作后,當達到突發長度或者突發終止指令出現時,SDRAM控制器將終止其操作。

通過SDRAM控制器模塊的控制傳輸,可以將采集到圖像數據實時的傳輸到存儲器件暫存。采用控制器模式具有一定的通用性,DSP可以通過控制器模塊直接讀取存儲圖像數據進行分析處理。

2.4 DSP子系統

DSP接收預處理模塊輸出的降了分辨率的Bayer RGB格式數據到數據緩存器,再將緩存數據傳到片內preview engine模塊進行格式轉換,將Bayer RGB格式圖像數據轉換為YUV422格式數據。DSP對YUV422格式數據進行壓縮處理后送到輸出端口輸出。

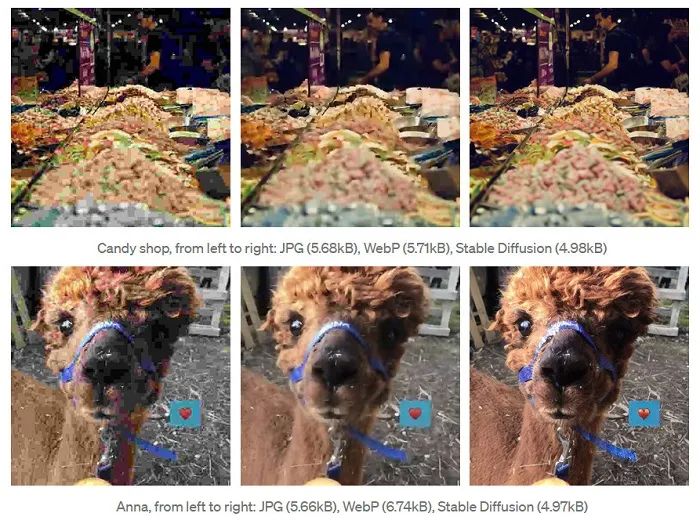

DSP通過SDRAM控制器讀取SDRAM中的高清原始數據,進行一些智能化分析處理,如識別、驗證等。根據處理結果和系統設定的閾值如光強變化、動靜變化等,決定是否對當前或者前幾幀圖像進行傳輸。高清圖像數據傳輸由DSP通過一定的相關處理結合到輸出數據流中傳輸到后端,由后端提取出高清原始數據,進行各種應用。

3 結語

采用了FPGA和DSP技術,設計了對CMOS圖像傳感器進行圖像采集和處理系統。該系統直接對CMOS傳感器進行原始數據的采集,為后繼處理的靈活性和應用的多樣性做好數據基礎。在FPGA中將數據分成兩路,一路作為原始數據暫存到SDRAM,一路按照傳統的處理、輸出。這樣既能實現了傳統圖像采集處理系統的功能,又能保存原始的數據為進一步的應用開發提供了硬件基礎,能較好地解決網絡傳輸帶寬不足與關鍵時刻或者關鍵場景需要高分辨率圖像進行分析處理的矛盾要求。采用FPGA+DSP的硬件組合具有相當大的靈活性,后期功能開發潛力大,可以根據不同的軟件配置,實現多種功能,具有良好的應用前景。

評論