基于GPIB和計算機并行口的SoC自動化測試方案

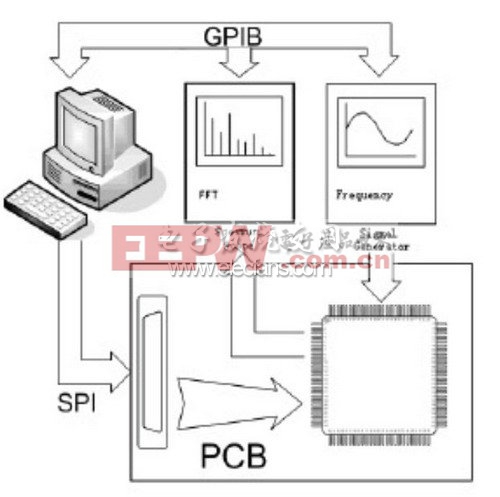

利用之前設計的硬軟件模塊可以完成SoC自動化測試。圖2為測試系統框架,

圖2 測試系統框架

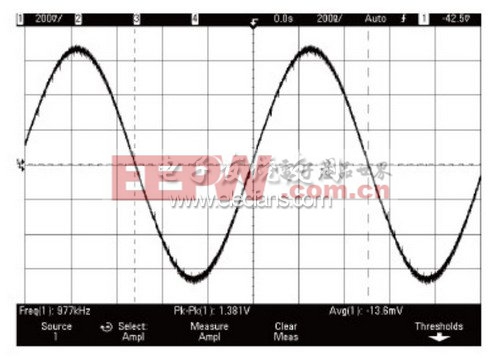

圖3為利用該系統測試得到的一個數模轉換器輸出信號的時域波形,

圖3 合成信號時域波形

圖4所示為利用該系統得到的該信號的頻譜特性。

圖4 合成信號頻譜特性

通過相關的GPIB接口總線對設備的控制指令控制頻譜儀,可以使頻譜的捕捉在4秒鐘內完成,整個測試流程在1分鐘內完成,有效地節約了測試時間。在多片測試中,測試員啟動批處理文件就可以完成快速測試流程。對比傳統測試方案,該方案不需要反復更換測試儀器探頭及調試測試儀器,只需要更換開關電源及待測芯片即可。

評論