網絡處理器的發展及應用

我們所熟悉的通信網的基本結構是由傳統的電路交換系統和基于分組的交換系統構成,整個網絡都是由一系列小的網絡、傳輸和終端設備組成, 網絡之間互通性差、可管理性不強,網絡業務不靈活。隨著電子商務、多媒體業務和VoIP等業務的出現對帶寬的要求越來越高,同時,對網絡業務流量的控制能力和網絡安全也提出了更高的要求。

為適應這些網絡需求,當今網絡正在向NGN(Next Generation Network)的方向發展,下一代網絡是可以提供包括話音,數據和多媒體等各種業務的綜合開放性網絡構架,采用開放的網絡構架體系、業務驅動的網絡、基于統一協議的基于分組的網絡。這就要求各設備、芯片制造商開發生產出適應性更強、功能更強大的相關設備以滿足網絡發展的需求。而具有可編程性、強大處理能力的網絡處理器NP(Network Processor)正是適合成為這些設備的核心功能單元。

網絡處理器的發展

網絡設備如路由器和交換機的體系結構的發展基本上經歷了基于通用處理器的體系結構和基于ASIC、RISC的體系結構兩個階段。

基于網絡處理器的體系結構是在以上兩種體系結構的基礎上,綜合了雙方優點推出的一種新型的體系結構。網絡處理器是一種可編程ASIC,不但可為系統提供類似ASIC的處理速度,而且可以提供類似通用處理器的靈活性。網絡處理器主要被用于處理線速(wire-speed)數據,進行協議分析和數據分類,位于物理接口處理器和交換架構之間。

網絡處理器的功能特性

網絡處理器具備完全的可編程能力,可以實現OSI網絡協議棧2~7層的處理,對諸如信元、分組數據流等多種協議數據類型的支持滿足了邊緣設備的需要;同時簡單高效的編程開發特征為網絡處理器走向市場奠定了基礎;強大的處理能力可以實現高帶寬的線速處理;開放的高度集成的體系結構使得基于網絡處理器的網絡設備易于系統擴展。網絡處理器的主要任務是數據包的分析、處理及轉發,因而其主要的功能包括以下幾部分:

協議識別和分類:根據數據包的協議類型、端口號、目的地址、以及其它特定于協議的信息對數據包進行識別。

拆裝和重組:數據包的拆分,處理,以及為轉發而重組。

排隊和接入控制: 識別出數據包之后,將這些數據包送往相應的隊列中以進行下一步處理,如優先處理,流量整形等。同時,可根據某些安全接入策略進行數據包過濾,確定是繼續轉發,還是丟棄。

流量整形和流量工程: 某些協議或應用要求對流量進行整形以使之在進入輸出線或輸出光纖時滿足時延和時延抖動的要求。

QoS(Quality of Service)和CoS(Class of Service):除了對數據包進行流量整形外,數據包還可以被打上標簽送往下一網絡節點進行更加有效的處理。

修正數據包 :編輯數據包并添加額外的信息。

差錯檢測 :正確檢測來自數據鏈路層的有差錯的數據包并能采取有效的處理措施。

網絡處理器的體系結構

隨著Intel 和IBM等公司大舉進入網絡處理器市場,采用基于處理器體系結構的網絡處理器得到迅速發展,下面以Intel和IBM公司推出的網絡處理器家族中主流產品作一簡單介紹。

IXP1200網絡處理器是Intel 公司推出的互聯網交換架構的網絡處理器之一,它由一個StrongARM處理器、六個微引擎(Microenginer)、存儲器接口和高速總線接口組成。IXP1200的主要功能模塊和體系結構的主要特征:

并行處理器結構: StrongARM核和6個微引擎均為RISC處理器,并行工作,StrongARM核主要負責協議控制平面和上層應用程序的處理,6個微引擎是32位的可編程RISC,有各自獨立的控制存儲器和局部寄存器,訪問外部資源(SRAM、SDRAM和IXBUS等)的機會均等,提供大于2倍外部帶寬的內部總線帶寬。Intel 推出的微碼(Microcode)運行在微引擎上,微碼的可重載性為系統升級提供了極大的方便。

硬件多線程 : 微碼指令的運行采用5級流水線機制,同時考慮訪存延遲,為提高微引擎的利用效率,采用硬件多線程,即每個微引擎同時運行4個線程,采用內部線程通信機制實現線程同步,提高了系統效率。

分布式數據存儲和內存組織優化:IXP1200提供了多個存儲單元接口,利用專用的讀寫寄存器實現對SRAM和SDRAM的訪問,簡化了編程模型,提高了存儲效率。同時SDRAM和SRAM均支持多個讀寫隊列進行優先級排隊以優化帶寬。

可擴充的體系結構:IXP1200的IXBUS總線接口可以實現多個IXP1200的系統擴充。

Ixp1200網絡處理器提供了適應下一代網絡設備的開放的體系機構,IX BUS總線不僅作為數據通道外接Ethernet MAC 、ATM、E1 等器件,還可實現多個IXP1200的系統擴展。

PCI標準接口為系統開發調試提供了方便。多種存儲器接口為內部存儲訪問、數據表查找效率的提高提供了硬件基礎。

IBM公司在網絡處理器的開發上也推出了PowerNP 系列產品,如PowerNP 4GS3,能夠提供10/100 Ethernet、Gigabit Ethernet、POS等多個端口的連接,可以配置成40個10/100 Ethernet或者4個Gigabit 的端口,也可以配置成OC-48、4個OC-12端口,最高達到4Gbit的帶寬。IBM的網絡處理器同樣采用了基于處理器的結構,主要由以下幾部分組成:

EPC(Embedded Processor Complex)嵌入式處理器組:具備可編程能力的16個微處理器主要負責數據包的轉發處理。

入口EDS:對來自以太網物理層設備的幀進行入隊、出隊和調度,送往交換組織。

出口EDS:對來自交換組織幀進行入隊、出隊和調度,送往物理層設備。

入口和出口交換接口:完成中間交換或者與其他網絡處理器的內部連接。

入口、出口PMM(Physical MAC Multiplexer):分別接收、發送來自Ethernet、POS物理層設備的幀。

嵌入式PowerPC:作為控制CPU,主要負責整個網絡處理器的管理和控制,同時負責協議幀的處理。

IBM網絡處理器同樣具有可擴充能力,多個網絡處理器組成一個交換和路由系統,實現2、3層直至更高層幀的線速轉發處理(見圖1)。

網絡處理器的應用

基于其強大功能,網絡處理器可以被用于實現從邊緣網絡至核心網絡的一系列應用,如:

WAN/MAN 邊緣路由器;

多業務接入平臺:支持IP、ATM和MPLS;

企業網骨干交換機;

DSLAM和其他寬度應用設備,如3G無線基站、CMTS;

VPN網管/路由器;

防火墻和安全路由器;

IP 吉比特/太比特路由器;

IPv6路由器。

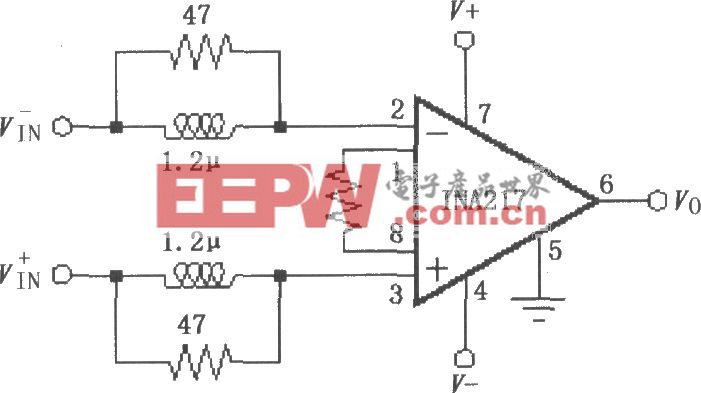

從概念上來看,以上所有的應用都是基于如圖2的體系結構,物理層把來自物理介質的光、電信號轉換成一定格式的比特流幀,幀轉交到網絡處理器,網絡處理器通過兩條通道處理數據幀,快速通道,如數據通道或者轉發通道,實現線速處理轉發數據幀,這部分是由微引擎完成的;慢通道,如控制通道,完成小部分數據幀(如控制、信令、路由幀)的處理,這是由通用微處理器完成的。在采用背板交換的網絡設備中,由交換背板完成系統擴展和數據幀的交換。

下面以網絡處理器在IPv6核心路由器中的應用作一探討。IPv6路由器和IPv4路由器相比,主要的區別在硬件和軟件的實現方面。硬件需要支持IPv6的網絡處理器,以及更快速和更高容量的CAM(根據內容訪問的存儲器)存儲芯片,而這方面目前還缺乏成熟的產品。軟件方面需要對原有的協議棧進行重新實現,這將涉及大量的程序修改和編譯、調試工作,此外還需要增加一些新的協議和功能,如IDRP(域間路由協議)、即插即用支持、QoS的全面支持等。其中的難點和關鍵是網絡處理器。NPU在路由器中的角色相當于CPU在PC中的角色,它專門為網絡處理量身定制,以線速處理和轉發每個數據包,并且具有可編程能力,因此可以隨技術的發展而進行現場升級。

IBM網絡處理器同樣具有可擴充能力,多個網絡處理器組成一個交換和路由系統,實現2、3層直至更高層幀的線速轉發處理。圖2給出了兩個網絡處理器擴充的配置圖,兩個網絡處理器之間擁有全雙工的快速通道,可以配置成提供80個10/100 Mbps以太網端口,或者是60個10/100 Mbps以太網端口加上2個千兆口,同樣也可配置成8個千兆口。

核心路由器主要有百兆、千兆線卡、交換背板、交換板和主控模塊板組成,從圖3中看出4個線卡支持96個10/100Mbps以太網口,一個千兆的線卡支持6個千兆以太網口,其中交換模塊通過背板直接和各個線卡相連,另外加上一個控制模塊。

其中百兆的交換線卡模塊主要有2個IXP1200構成,其交換模塊為IXE2424,每個端口都有IPv6路由功能,千兆模塊主要有Intel第二代網絡處理器IXP2400構成,其交換模塊為IXE5416。

另外一個典型應用是開發基于網絡處理器的防火墻,利用網絡處理器的可編程能力可以容易實現防火墻的數據包過濾、訪問控制、入侵檢測、地址轉換等功能,并且可以在同一硬件平臺上對軟件升級以滿足不同用戶的需要。基于網絡處理器的防火墻是硬件防火墻,因此有線速處理能力。目前國外的廠商已經推出了基于網絡處理器的防火墻產品,我們國內的一些公司也正在加快這方面的開發與研究,相信很快就會有相應的產品問世。

結語

網絡處理器通過十分靈活的體系結構和強大的處理能力,將可編程能力和ASIC的處理能力有機的結合在一起,從而帶來更為智能的網絡設備、更短的產品研發周期以及更便捷的系統升級方式。各大廠商均推出了10Gbps的網絡處理器和其他的編程模型,40G 的網絡處理器正在逐步推向市場。網絡處理器論壇(Network Processing Forum, NPF)在公共交換接口協會和公共編程接口論壇的基礎上成立,加快了網絡處理器的發展步伐。在今后幾年里網絡處理器將迅速得以普及應用,代表著下一代網絡設備的核心功能單元,將有著非常巨大的發展空間。

參考文獻

1 Intel,Inc. Intel IXP1200(r) HW Ref Maunel.2001.8

2 IBM Network Processor product overview.www.ibm.com

3 System Requirement for Terbit Router Mehrdad Nourani.2001 IEEE

4 Architectures for Network Processing Joseph Williams.2001 IEEE

5 Agere,Inc. White Paper: Challenge for Next Generation Network Processors. 1999.9

6 PMC Inc. White Paper A New Architecture of Switch and Router Design.1999.12

評論