一款高效率的線性穩壓器

引言

為了滿足穩定性及啟動時大的浪涌電流要求,對穩壓器的壓降有嚴格的限制,而且還需配備體積較大、效率較低的輸出電容,因此多年來,在較高電流(超過 1A)的低輸出電壓應用中使用線性穩壓器一直都是個難題,現在可以利用 TI 的雙輸入軌 TPS74x01 來解決這些問題。

線性穩壓器拓撲結構概述

在較高電流應用中使用線性穩壓器的主要問題在于效率低下,其效率可通過 VOUT/VIN 計算得出。線性穩壓器中的功率損耗 (PLOST) 主要來自其封裝,該功率損耗可以通過如下公式計算得出:

![]()

TO-263 或 D2PAK 封裝是可用于線性穩壓器的最大表面貼裝封裝。如果不計氣流的話,該封裝的最大功耗大約為 2.75W(假設該封裝與一塊較大的銅板焊接在一起用于散熱)。許多配備了 PMOS 旁路元件的高電流“低壓降”線性穩壓器的最小輸入電壓范圍為 2.5V~2.7V,其不但可以為內部 LDO 驅動電路供電,而且還足以驅動 PMOS FET 來提供較高的輸出電流。

由于額外氣流和/或需要對穩壓器所產生的熱量進行外部散熱,因此,在輸出電壓低于 1.8V 和輸出電流大于 2.5A 時使用帶有 PMOS 旁路元件的線性穩壓器就會顯得不便,并且成本也會增加。

與類似的額定電流 PMOS FET 相比,NMOS FET 本身具有較低的 rDS(on),因此 NMOS FET 旁路元件只需較低的 VIN-VOUT 壓降即可提供相同強度的電流。然而,基于 NMOS 的穩壓器的源極跟隨器結構要求,FET 柵極電壓至少為一個高于輸出電壓的閾值壓降(通常為 1V)。穩壓器需要一個內部充電泵來提供更高的柵極驅動電壓,或一個由電路中現有的 5V 或 3.3V 偏置電源產生的二次低功耗輸入軌,這就是開發雙輸入軌、基于 NMOS 旁路元件的 TPS74x01 系列線性穩壓器的原因。

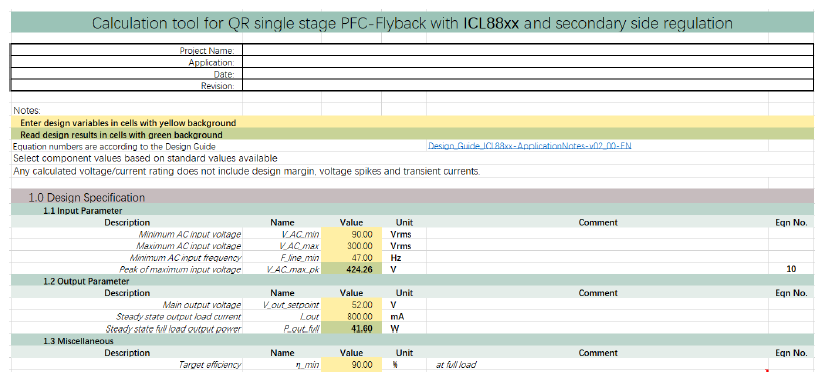

壓降

如圖 1 所示,TPS74x01 穩壓器具有兩個輸入電壓,其中一個用來提供低電流偏置電壓以驅動控制 NMOS 旁路器件的內部電路,另一個用來進行二次功率輸入。由于所有的內部電路均使用較高的 BIAS 輸入電壓運行,因此旁路元件可以通過一個低壓輸入電源實現穩壓。實際上,輸入功率 IN 只受輸出電壓和器件壓降的限制。

圖 1 TPS74201 和 TPS74401 線性穩壓器的結構圖

TPS74x01 有兩種不同的壓降規范,第一種被稱為 VIN 壓降,其專門針對那些希望通過使用外部偏置電壓來實現低壓降的用戶。該規范假設了 VBIAS 至少比 VOUT 高 1.62V。此類應用中,FPGA 收發器一般使用低紋波、1.2V、3A 的電源軌,該收發器內部 1.5V 和3.3V 的開關電源分別提供輸入電壓和偏置電壓。在此結構中,55℃ 時功耗為 1.9W 的 33mm QFN 封裝功耗僅為 (1.5V-1.2V)3A=0.9W,從而達到了 1.2V/1.5V=80% 的效率。

第二種規范被稱為 VBIAS 壓降,該規格的壓降專門針對那些希望將 IN 和 BIAS 引腳綁定在一起的用戶。這樣就可將該器件用于無輔助偏置電壓或不要求低壓降的應用中。因為 VBIAS 要為旁路 FET 提供柵極驅動,所以 VBIAS 必須要比 VOUT 高 1.4V,同時壓降受限于應用中所使用的 BIAS。例如 TPS74201 可通過一個效率為 66%(3.3V/5V)的 5V 電壓軌提供一個 3.3V、1.0A的軟啟動電源(稍后將作討論),并且功耗為:

(5V-3.3V)1.0A=1.7W

穩定性和瞬態響應

由于輸出電容與負載阻抗生成的其中一個控制環路極點的頻率位置會隨著輸出電流的變化而變化,到目前為止,線性穩壓器環路穩定性對模擬 IC 設計人員而言還是一個難題。在源跟隨器結構中,具有 NMOS 旁路元件的穩壓器更易于實現功率補償,因為在共源結構中,其輸出阻抗低于相近功率的PMOS穩壓器。這就意味著 NMOS 穩壓器的移動極點頻率高于同類額定功率 PMOS,即遠遠高于內部誤差放大器極點。確保穩定性的傳統方法,一是在低頻下逐步減少控制環路的響應,從而減少瞬態響應;二是利用具有若干等效串聯電阻 (ESR) 的輸出電容產生的零電位抵消移動極點。采用專利反饋控制拓撲技術的 TPS74x01 系列的 VBIAS 為 3.3V、VIN 為 1.8V 并且 VOUT 為 1.5V,無需輸出電容即可實現快速瞬態響應(請參見圖 2),同時在與具有 ESR 的較大電容共同工作時仍然能保持穩定。在負載瞬態之后沒有輸出電壓振鈴,這表明穩壓器在沒有輸出電容的情況下非常穩定。

圖 2 采用各種輸出電容時的負載瞬態響應

由于 TPS74x01 系列產品在沒有輸出電容的情況下比較穩定,且瞬態響應比較快,該功率器件的本地旁路電容可以滿足許多 FPGA 以及 DSP 的要求。因此,由于不再需要用于電源軌的大型電容器,從而降低了解決方案的總成本。

軟啟動和排序

許多傳統的線性穩壓器啟動速度均較快,這是因為其反饋環路可以感應到低輸出電壓并開啟旁路 FET。對于某些應用而言,快速啟動是必要的,但是這樣的快速啟動會引起較大的浪涌電流(浪涌電流甚至達到了該器件的額定電流極限值),并對輸出電容進行充電。該高電流可能會破壞輸入電源總線,并且會導致一些系統級故障。為了實現可減少啟動過程中的峰值浪涌電流并最小化輸入電源總線監控的啟動瞬態的線性、單調的軟啟動,TPS74201 和 TPS74401 誤差放大器將對外部軟啟動電容的電壓斜坡值進行跟蹤,直到電容器電壓超過內部參考電壓。軟啟動斜坡時間取決于軟啟動充電電流 (ISS)、軟啟動電容 (CSS) 以及內部參考電壓 (VREF),其計算公式如下:

![]()

需要注意的是,由于軟啟動是壓控的,所以啟動與輸出負載無關。

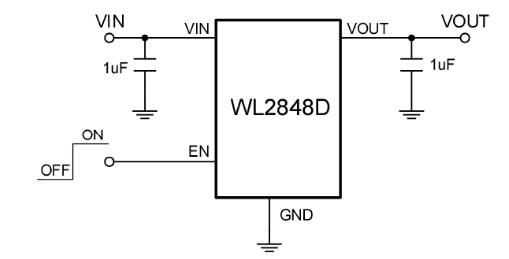

TPS74301 版本采用 TRACK 引腳,而不是 SS 引腳。如圖 3 所示,在一個連接至 TRACK 的外部電源,使用一個電阻分壓器中心抽頭,TPS74301 的輸出電壓將跟蹤外部電源直至 TRACK 電壓達到 0.8V。該特性可用于實施同步或比例排序。該特性還有助于最小化 ESD 結構中 Core 和許多處理器 I/O 電源引腳和/或管理集成上電復位電路之間的應力。通過將集成的 PG 信號連接至跟隨電源的 EN 引腳,所有 TPS74x01 系列產品均可簡化順序排序的實施。

圖 3 采用 TRACK 引腳的各種排序方法

結論

TPS74x01 系列產品均帶有一個雙輸入軌并具有低壓降的特點,該系列產品使線性穩壓器比開關穩壓器更勝一籌,其不但能夠減小電路板的尺寸并降低成本,還可以高效地提供許多較低電壓和更高輸出電流的電源軌。該系列產品還擁有其他的一些特性,其中包括可控軟啟動、跟蹤和集成 PG,可以處理過去一直困擾線性穩壓器的啟動問題。再加上可最少化輸出電容總數量的快速瞬態響應等特性,該器件可幫助您擁有近乎理想的DC/DC 轉換器。

評論