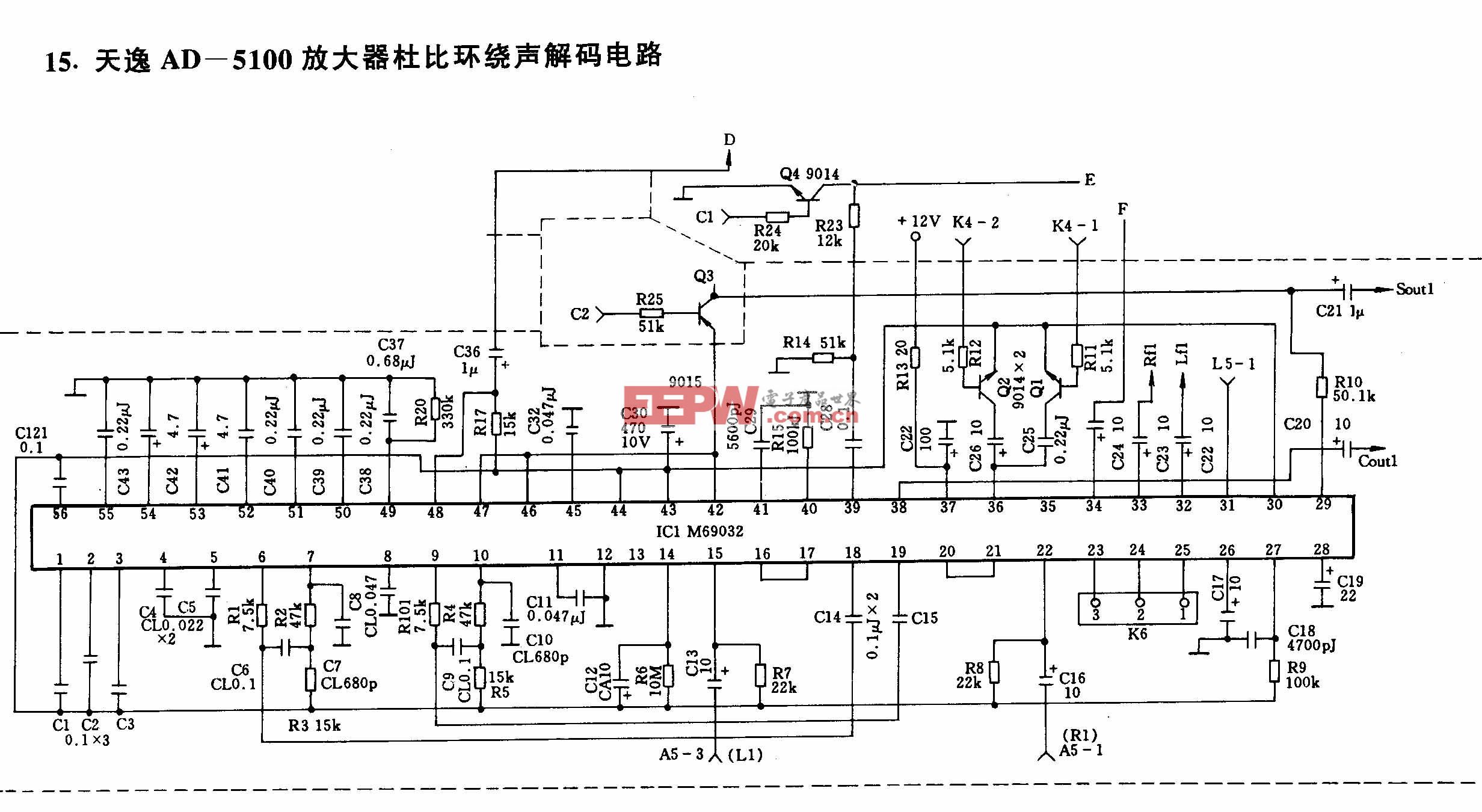

基于AD9516的高速四通道時間交叉采樣時鐘的設計

隨著數字信號處理的高速發展,模擬信號的處理已被數字化處理代替。但對數字系統分辨率的日益提高,作為模數轉換系統的核心一A/D轉換器,其精度和采樣率也隨之提高。但精度和采樣率是一對矛盾體,很難同時滿足要求,因此成為制約A/D采樣系統發展的瓶頸。時間交叉采樣方案的提出,突破了單個A/D轉換器性能的局限性,采用多片高速A/D轉換日歷交替采樣是一種提高系統采樣率的有效方法。在多片并行A/D轉換器采樣系統中,信號重構對于采樣時鐘精度要求相當嚴格,傳統的晶體振蕩器加移位電路和濾波電路的模擬方式已不能滿足這一要求。本文提出基于時鐘分配器AD9516向四路時間交叉A/D轉換器提供采樣時鐘。

2 器件簡介及其配置

2.1 AD9516簡介

AD9516是一款集低相位噪聲時鐘發生和低抖動14通道時鐘分配功能于一體的時鐘分配器。其內部集成1個整數N分頻的頻率合成器、2個參考輸入端、1個壓控振蕩器(VCO)、可調延遲線和14個時鐘驅動器,還包括LVPECL、LVDS和CMOS輸出。另外,片內集成的VCO可提高系統可靠性。14個輸出通道分別為6路(3對)時鐘可高達1.6 GHz的LVPECL輸出和4路(2對)時鐘高達800 MHz的LVDS輸出,LVDS時鐘輸出可選為高達200 MHz的兩通道CMOS輸出。

2.2 引腳說明及外圍電路配置

REN_SEL:參考選擇。AD9516有REFl和REF2兩個參考時鐘輸入端,該引腳用于定義系統是采用REFl輸入(拉低)還是REF2(拉高)的參考信號。

SCLK,CS,SDI0,SD0:串口同步I/0,與SPI協議相兼容,實現與AD9516內部寄存器的通信。其中SCLK為時鐘輸入;CS為片選信號;SDIO為主機輸出/AD9516輸入(SCLK的上升沿),或者主機輸入/AD9516輸出(SCLK的下降沿);SDO為主機輸入/

AD9516輸出。

REFMON,LD,STATUS:狀態輸出,用于測試AD9516內部信號。通過改變0x17,0x1A,0xlB(內部寄存器的地址)3個寄存器.測試VC0及分頻器的輸出時鐘,獲得當前AD9516工作狀態。

LF,CP:外部環形濾波,可向內部VCO提供反饋電壓。

OUT6,OUT6,0UT7,OUT7,0UT8,OUT8,OUT9,OUT9:輸出四路LVDS時鐘,可向A/D轉換器提供采樣時鐘。

以上為AD9516主要引腳的功能描述,還有一些包括輸入電壓,復位等引腳的功能描述可見參考文獻。根據上述主要引腳描述,給出了AD9516的外同電路配置圖,如圖l所示。

2.3 內部寄存器配置

AD9516可設置3種工作模式,包括外部VC0、外部CLK以及內部VC0。本系統設計采用內部VCO和參考輸入頻率工作模式。

2.3.1 PLL的工作原理

參考輸入(REFl輸入)先經R分頻模塊(14位寄存器),再通過R延時模塊(延時可調節)后進入PFD(相位/頻率監測)模塊一端,同時VCO產生的信號通過N分頻模塊(預分頻模塊P.P+1和A/B計數模塊)和N延時模塊(延時可調)后進入PFD的另一端;PFD用于比較兩信號的頻率和相位差.產生與之成比例的信號傳輸給CP(電荷泵),電荷泵通過外接環形濾波器連接至VC0的控制端。電荷泵根據PFD的信號對環形濾波器的連接節點充(放)電以達到VCO電壓調節目的,使VCO輸出和參考輸入與PFD的頻率和相位完全匹配,此時鎖存相位,輸出同步。

2.3.2 分頻寄存器的配置

除了PLL用于產生穩定的VCO所涉及的寄存器R,A和B外,分頻寄存器還包括時鐘輸出分頻寄存器,每對兒輸出通道的分頻寄存器。時鐘輸出分頻器可以隨意設置為2~6中的任意整數,輸出通道的每個分頻器可選用1~32中的任意整數作為分頻參數。需要注意的是:PLL的R、A和B這3個寄存器的配置相互制約,必須合理配置VCO才能工作在由參考輸入提供的頻率范圍內,否則將導致不能鎖存鎖相模塊。這些制約包括:PFD(相位/頻率監測)輸入頻率范圍、A和B計數器輸入最高頻率、A和B值大小。設計時,考慮到這些制約以及設計的需要就能正確配置內部分頻寄存器。

2.3.3 輸出相位寄存器配置

調整輸出相位:包括相位延時粗調和相位延時細調。

(1)相位延時粗調

由于系統要求相差為90的四路110 MHz采樣時鐘。OUT6作為相位的基準信號,則OUT7相對延時90,OUT8相對延時180,OUT9相對延時270。由于四路LVDS輸出是2對,每對共用2個分頻器。OUT6與OUT7共用,OUT8與OUT9共用。AD9516的分頻器可選用相位延時,因此,可把OUT8與OUT9共用的分頻器設置為相位延時180,則在相位細調時,只需調整0UT7延時90,OUT9延時90即可。

(2)相位延時細調

對于OUT7與OUT9相對于OUT6與OUT8的延時90,通過調節每個輸出通道的AT微小延時模塊來實現,相位延時細調是通過對△T模塊內的電容充放電獲得,延時時間可通過電容量和電流值計算。

3 軟件編程

根據AD9516的工作原理,正確配置所有寄存器,需要把數據加載到AD9516內部寄存器。AD9516的加載模式為串口同步加載,兼容于SPI標準協議和SSR協議,串行控制端允許對AD9516所有寄存器的配置進行讀/寫,支持單字節和多字節及高/低位優先順序模式,AD9516串行控制可以配置為單一的雙I/O引腳(SDIO)或兩個單向引腳(SDIO/SDO)模式。默認模式下,AD9516為雙端模式加載,加載時鐘為SCLK。

為了便于調試,DSP作為整個讀寫操作的核心,不管是讀數據還是寫數據都由DSP完成。寫AD9516的軟件流程是先把寫入寄存器的數值存放在FPGA的ROM中,由DSP通過慢速協議從FPGA讀取數據.然后通過DSP寫入FPGA的寫模塊,最后寫入AD9516。而讀AD9516的軟件流程是根據AD9516的讀時序,寫入讀指令,最后由讀模塊讀取AD9516的寄存器數值。具體FPGA設計如圖2所示。

在完成FPGA設計后,由于整個系統控制都是由DSP完成,因此需對DSP進行編程。以下給出部分DSP(TS一201)的寫AD9516的程序代碼,其中系統寄存器配置為0X189067:64位總線,慢速協議。

最后根據FPGA設計,利用Quartus II仿真,寫AD9516模塊的軟件仿真如圖3所示。FPGA采用Ahera公司的STRATIXTM II系列的一款EP2S60F672器件。其仿真結果與AD9516的寫時序完全吻合。

4 結語

交叉采樣系統時鐘源性能是決定整個采樣系統指標的關鍵。基于此,本文提出了利用AD9516給高速A/D轉換提供采樣時鐘的設計方案。實踐證明,利用這種方法產生的時鐘能夠滿足四通道A/D轉換實現440 MHz的交叉采樣的時鐘要求,可供其他高速A/D轉換的設計人員借鑒。

評論