基于TLV1562的四通道高速實時數據采集系統的設計

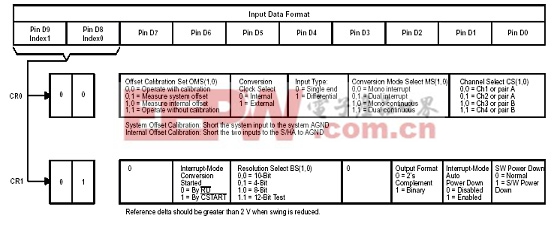

由于TLV1562芯片是可配置A/D轉換器,其配置轉換時序圖見圖。所以如何利用CPLD實現對TLV1562的配置與讀寫是關鍵技術之一。對于TLV1562的讀寫控制易于實現,而對于其配置,由于是對四通道循環采集,較為復雜。在TLV1562中有兩個寄存器需要配置,也就是要有兩次寫,而每次配置的數據還不一樣(見表一),所以應該在每次寫的時候都應相應的提供數據。整個配置過程用VHDL語言采用有限狀態機的方式來實現。定義5個狀態,分別為st0,st1,st2,st3,ST4,st0是空閑態,st1,st2,st3,ST4是對應相應采集通道的狀態,INDEXREG[1..0]是用來監測寫信號的第幾次寫的標識碼。 程序如下:

type states is (st0,st1,st2,st3,ST4);

signal current_state,next_state :states :=st0;

signal indexreg:STD_LOGIC_vector(1 downto 0);

signal chanel_data: STD_LOGIC_vector(9 downto 0);

begin

indexreg=index_reg; cs=not start;

process(current_state,indexreg,ad_ale)

begin

if ad_ale='0' then

chanel_data=ZZZZZZZZZZ;

else

if indexreg=10 then

chanel_data=0100000100;

else

case current_state is

when st0=>ad_end='0'; chanel=00;

next_state=st1;

chanel_data=0011000000;

when st1=> ad_end='0';chanel=01;

next_state=st2;

chanel_data=0011000001;

when st2=> ad_end='0';chanel=10;

next_state=st3;

chanel_data=0011000010;

when st3=> ad_end='1';chanel=11;

next_state=st0;

chanel_data=0011000011;

when st4=> next_state=st0;

chanel_data=0011000000;

when others=> ad_end='1'; next_state=st0;

chanel_data=0011000000;

end case;

end if;

end if;

end process;

|

| 表一 控制寄存器配置表 |

3 結束語

文中詳述了基于TLV1562和EP1K100的多通道高速采集系統的設計及實現方法,將該采集系統應用到雷達數字式對消器中,結果證明精度和速度都能滿足要求。實現了在較低的成本下實施多通道數據采集處理。

評論