高速流水線浮點加法器的FPGA實現

現代信號處理技術通常都需要進行大量高速浮點運算。由于浮點數系統操作比較復雜,需要專用硬件來完成相關的操作(在浮點運算中的浮點加法運算幾乎占到全部運算操作的一半以上),所以,浮點加法器是現代信號處理系統中最重要的部件之一。FPGA是當前數字電路研究開發的一種重要實現形式,它與全定制ASIC電路相比,具有開發周期短、成本低等優點。但多數FPGA不支持浮點運算,這使FPGA在數值計算、數據分析和信號處理等方面受到了限制,由于FPGA中關于浮點數的運算只能自行設計,因此,研究浮點加法運算的FPGA實現方法很有必要。

1 IEEE 754單精度浮點數標準

浮點數可以在更大的動態范圍內提供更高的精度,通常,當定點數受其精度和動態范圍所限不能勝任時,浮點數標準則能夠提供良好的解決方案。

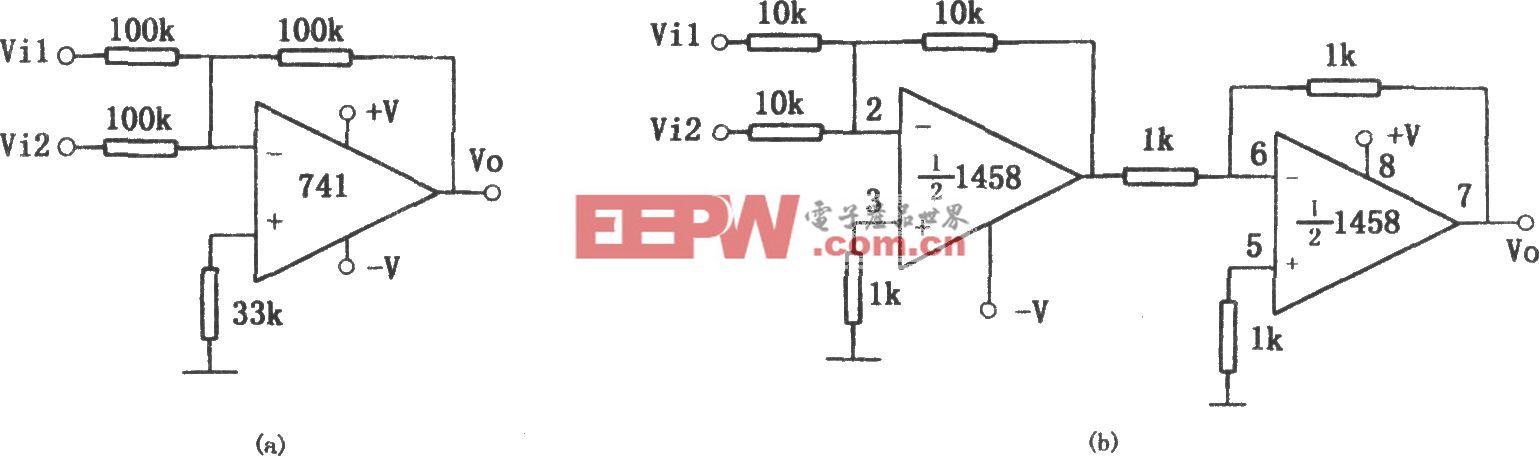

IEEE協會制定的二進制浮點數標準的基本格式是32位寬(單精度)和64位寬(雙精度),本文采用單精度格式。圖1所示是IEEE754單精度浮點數格式。圖中,用于單精度的32位二進制數可分為三個獨立的部分,其中第0位到22位構成尾數,第23位到第30位構成指數,第31位是符號位。

實際上,上述格式的單精度浮點數的數值可表示為:

上式中,當其為正數時,S為0;當其為負數時,S為1;(-1)s表示符號。指數E是ON255的變量,E減127可使指數在2-127到2128變化。尾數采用科學計算法表示:M=1.m22m21m20……m0。m22,m21,…,m0,mi為Mp的各位,設計時應注意尾數中隱含的整數部分1。0是一個特殊的數,0的指數位和尾數位均為0,符號位可以是1,也可以是0。

2電路的流水線結構

一般情況下,結構化設計是電路設計中最重要的設計方法之一,采用結構化設計方法可以將一個復雜的電路分割為獨立的功能子模塊,然后按一定的原則將各子模塊組合成完整的電路,這幾乎是電路設計的通用模式。這種設計方法便于設計人員分工合作、實現設計和功能測試,縮短上市時間、升級和二次開發,因而具有其它方法無法比擬的優勢。

結構化設計基本上可歸結為兩種方法:流水線(pipeline)和握手原則。其中握手原則適用于各功能子模塊內部運算比較復雜、數據運算時延(latency)不確定的設計。由于數據運算時延不確定,所以,各子模塊間的時序配合必須通過握手信號的交互才能完成。握手原則設計的電路一般采用復雜的有限狀態機(FSM)作為控制單元,工程設計難度大,故在設計時應慎重使用。流水線法適用于各功能子模塊內部運算簡單整齊、數據運算時延確定的設計。由于數據運算時延比較確定,各前后級功能子模塊不需要任何交互信號就能完成時序配合,故可方便地實現數據的串行流水運算。流水線控制比較簡單,一般不需要設計專門的有限狀態機,而且工程設計容易,設計時可優先選用。

3 工程的FPGA實現

3.1開發環境和器件選擇

本工程開發可在FPGA集成開發環境QuartusII 8.0 spl中完成。OuartusⅡ是世界著名PLD設計生產廠商――Altera公司的綜合性PLD開發軟件,內嵌綜合器和仿真器,并有可與第三方工具協作的靈活接口,可以完成從設計輸入到硬件配置的完整PLD設計流程,而且運行速度快,界面統一,功能集中,易學易用。

本設計中的器件選用Stratix IIEP2S15F484C3。Stratix II是Altera公司的高性能FPGA Stratix系列的第二代產品,具有非常高的內核性能,在存儲能力、架構效率、低功耗和面市及時等方面均有優勢。

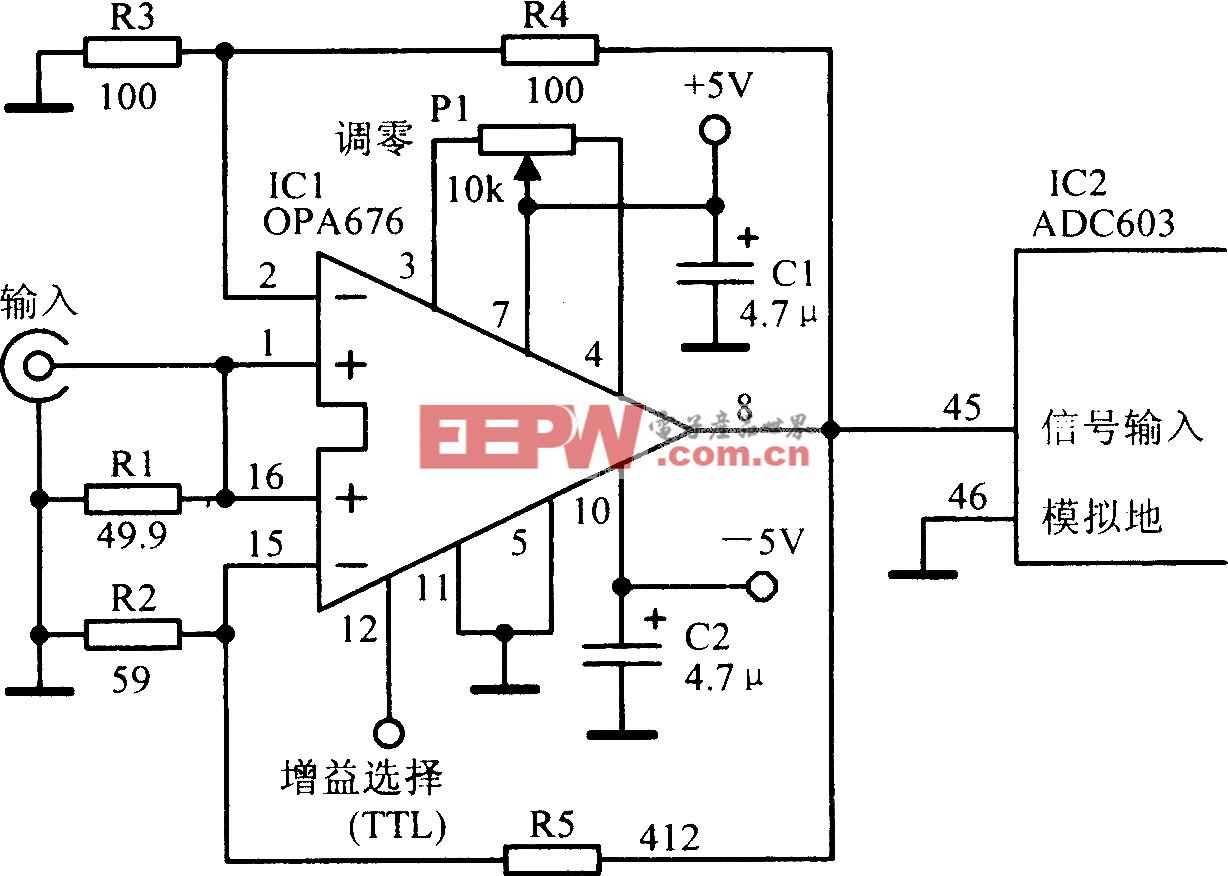

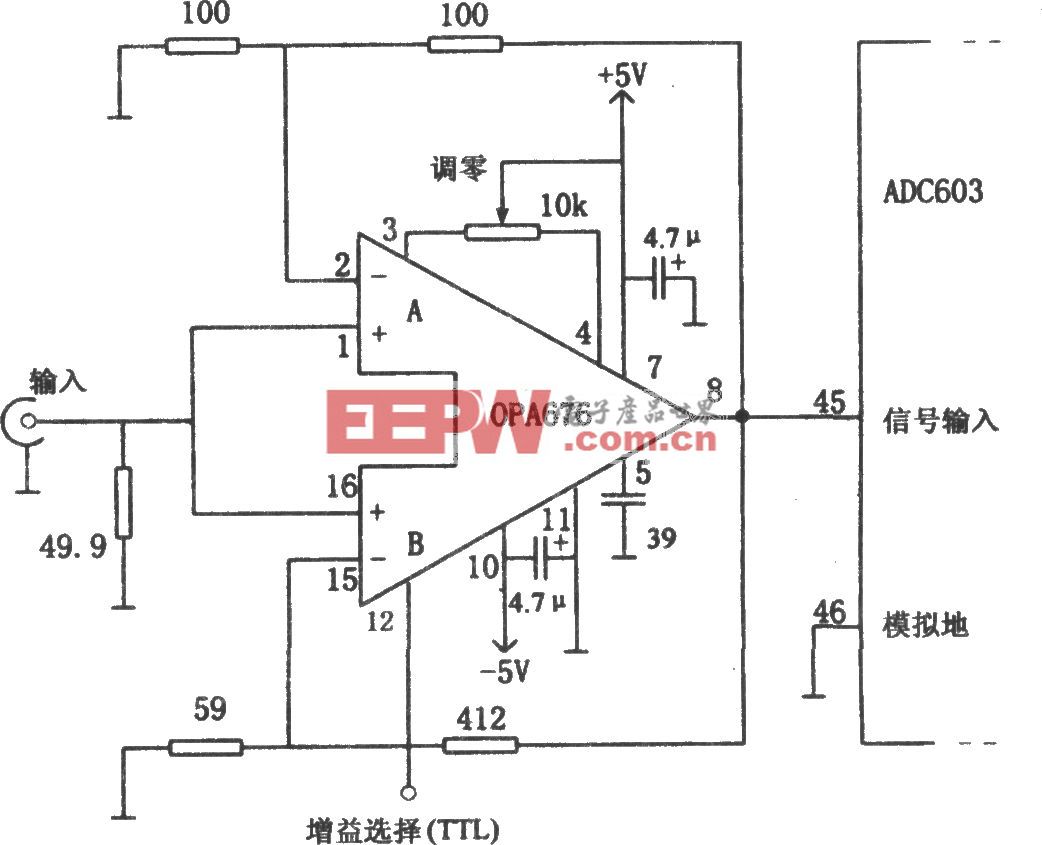

本系統的頂層框圖如圖2所示。為了顯示清楚,圖2被分成兩個部分顯示。本工程采用異步置位的同步電路設計方法,其中clk、reset、enab分別為系統時鐘、系統異步置位、系統使能信號。din_a、din_b分別為兩個輸入的單精度浮點數,data_out則是符合IEEE 754標準的兩輸入浮點數之和。

評論