利用數字電位計AD5292構建30V低成本DAC

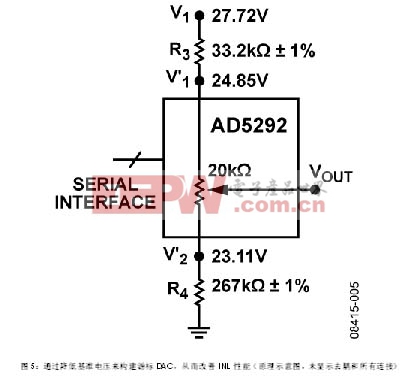

為改善電路精度,可以用兩個外部電阻降低AD5292上的基準電壓,如圖5所示,由此便可在有限的電壓范圍內提供全部10位分辨率(游標DAC)。數字電位計通常具有±20%的端到端電阻容差誤差,由于數字電位計與外部電阻之間存在匹配誤差,因此會影響電路精度。AD5292則具有業界領先的±1%電阻容差性能,有助于克服電阻匹配誤差問題。

本文引用地址:http://www.j9360.com/article/187750.htm

本文引用地址:http://www.j9360.com/article/187750.htm

圖5:通過降低基準電壓來構建游標DAC,從而改善INL性能(原理示意圖,未顯示去耦和所有連接)

這種情況下:

![]()

![]()

縮小范圍內的1 LSB可以通過下式計算:

![]()

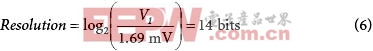

相對于最高基準電壓V1,游標DAC的等效分辨率為:

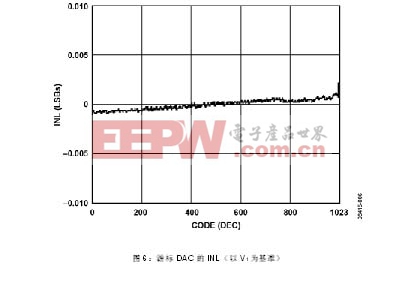

圖6顯示利用圖5的游標DAC電路而獲得的INL(以 V1為基準)曲線。

圖6:游標DAC的INL(以V1為基準)

AD5292具有一個20次可編程存儲器,可以在上電時將輸出電壓預設為特定值。

為了使本文所討論的電路達到理想的性能,必須采用出色的布局、接地和去耦技術(請參考教程 MT-031 和教程 MT-101)。至少應采用四層PCB:一層為接地層,一層為電源層,另兩層為信號層。

|

常見變化

AD5291 (8位、內置20次可編程上電存儲器)和AD5293(10位、無上電存儲器)均為±1%容差數字電位計,同樣適合本應用。

4.096 V低成本基準電壓源ADR5044也不失為一種選擇。R1/R2比值可以根據不同的基準電壓進行適當調整。

評論