數字音頻傳輸系統的設計與實現

CS5381是CirrusLogic公司推出120 dB、192 kHz高性能24 bit立體聲模數轉換芯片。CS5381可工作在主、從兩種模式下。模式選擇可通過管腳2 (M /S)來進行,本設計工作在主模式。CS5381采樣率可以通過MD IV、M0和M1這3個管腳邏輯電平控制,主時鐘選擇可以根據所選的采樣頻率和MD IV引腳作選擇。本設計中選擇的是48 kHz單倍速采樣率,采用12. 288MHz有源晶振做時鐘源。CS5381轉換結果是24位補碼形式串行數據,且左右通道交替輸出,可用LRCK高低電平來進行區分。輸出數據有兩種格式即左對齊和I2S格式,本設計采用I2S格式。

數字音頻的格式編碼與發送由Cirrus Logic公司的數字音頻發射器CS8406完成。CS8406可支持192kHz采樣率,并滿足下一代音頻格式,可接收和編碼音頻和數字數據,再經過多路復用和編碼后,將其傳送至電纜/光纖接口處。

器件的工作模式選為硬件模式(H /S = 1) ,輸入數據格式為I2S ( SFMT1 = 0, SFMT0 = 1 ) , 主時鐘頻率OMCK選為256 ×FS (HWCK1 = 1, HWCK0 = 1) 。IL2RCK、ISCLK、SD IN是來自CS5381的左右時鐘信號、串行時鐘信號和音頻數據; TXN、TXP是串行數據輸出端,通過這兩個引腳發送出編碼好了的AES/EBU 格式數據。

3. 3 接收端電路設計

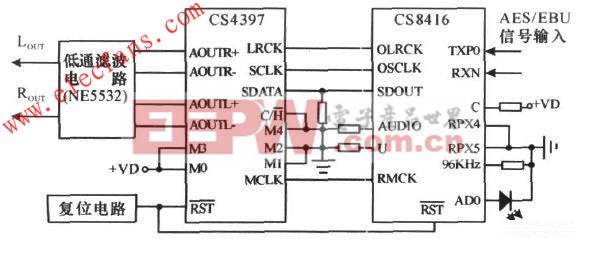

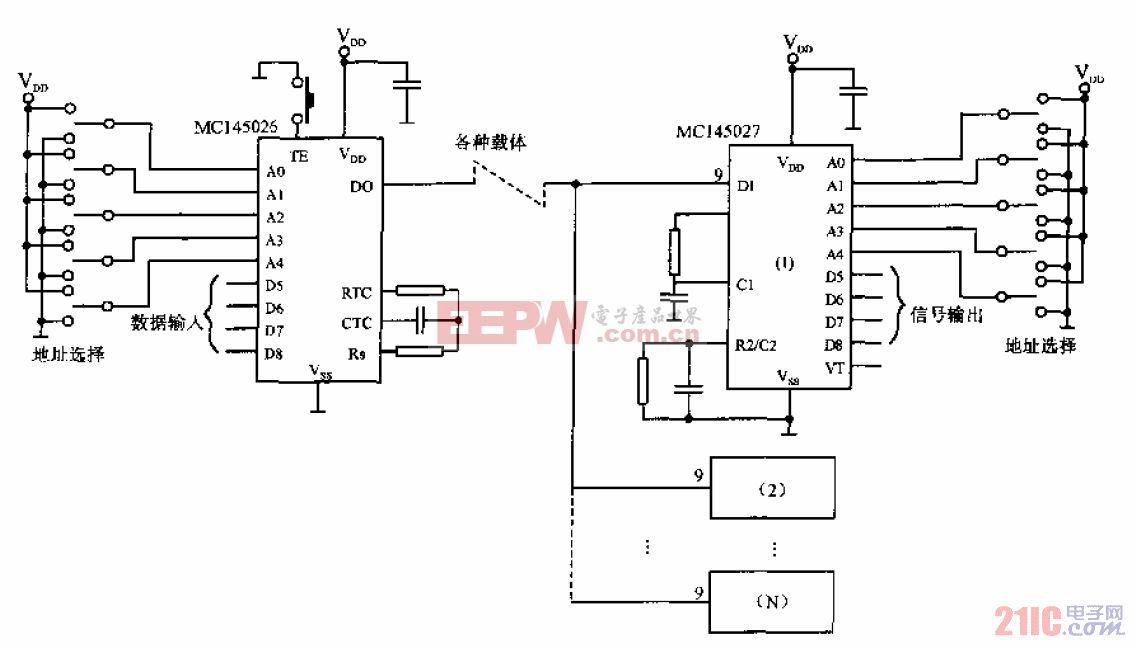

接收端電路我們選用與CS8406對應的數字音頻接收電路CS8416完成AES/EBU 格式音頻數據的接收和解碼,采用CS4397完成數字音頻信號至模擬信號的轉換,電路原理如圖3所示。

圖3 接收端原理圖。

CS8416是業界領先的192 kHz數字音頻接收器,具有200 p s的極低抖動性能。CS8416接收和解碼數字音頻數據的采樣頻率高達192 kHz,并采用一個極低的抖動時鐘恢復裝置,從進入的音頻流中產生一個清晰的恢復時鐘。一個8∶2輸入多路器允許多達8個數字音頻輸入源,多路器的第二輸出提供一個SPD IF直通特性,增添了系統靈活性。CS8416集成了壓縮音頻輸入流的自動檢測和CD - Q子碼解碼功能,并允許信號可選擇通往3個通用輸出(GPO)引腳。

工作在軟件模式下,在CS8416中可以同時接入8路數字音頻信號,當SDOUT對地接47 kΩ 電阻時,器件工作在硬件模式下,此時RXP4、RXP5、RXP6、RXP7將工作在第二功能下,用它們來設置所選定RXP0、RXP1、RXP2、RXP3做為接收引腳。在本設計中接收端只有一路合成的左右聲道數字音頻信號,所以我們選擇RXP0和RXN做為接收引腳(相應的設置RXP4= 0 RXP5 = 0) ,其他不用的接收引腳懸空; AD0是信號接收確認引腳,它連接一個發光二極管,當沒有接收到信號時,發光二極管亮,接收到信號時,發光二極管滅。OLRCK、OSCLK、SDOUT是在AES/EBU數據中提取出來的左右時鐘信號、串行時鐘信號和音頻數據。

AUD IO是非音頻數據流指示引腳,也是輸入數據格式選擇位SFSEL1; C (19腳)是通道狀態指示位,也是輸入數據格式選擇位SFSEL0。這兩個引腳通過47kΩ電阻接地或接高電平可以決定輸出數據的格式。圖3中接法選擇的是I2S 24 bit數據格式。U為用戶數據位,通過47 kΩ 電阻接地,選擇恢復主時鐘頻率MRCK為256 ×FS。

CS4397是Cirrus Logic公司推出一種完善的高品質24位48 /96 /192千赫立體聲數字至模擬轉換芯片。

評論