基于DAC5687的高速多通道信號模擬器設計

1 引 言

DAC5687是美國TI公司出品的一款雙通道、16bit高速數模轉換芯片。片內資源豐富, 具有內插、調制等多種功能。FPGA 因其屬于大規模在系統可編程專用集成電路而且具有高密度、高速度、高可靠性等特點, 因此FPGA 應用于高速多通道雷達信號模擬器可大大提高系統設計的靈活性和系統的擴展性。

本文設計的高速多通道信號模擬器系統可廣泛應用于通信、雷達信號的模擬產生, 為雷達設備, 特別是接收機設備檢修提供參考信號, 分離設備故障問題, 簡化設備檢修過程。另外, 此高速多通道信號模擬器系統基于CPC I總線, 具用很好的工程穩定性和通用性。

2 系統概述

2. 1 系統組成

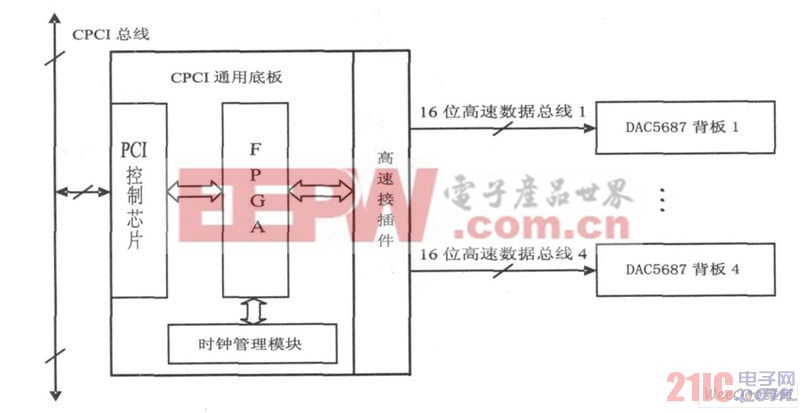

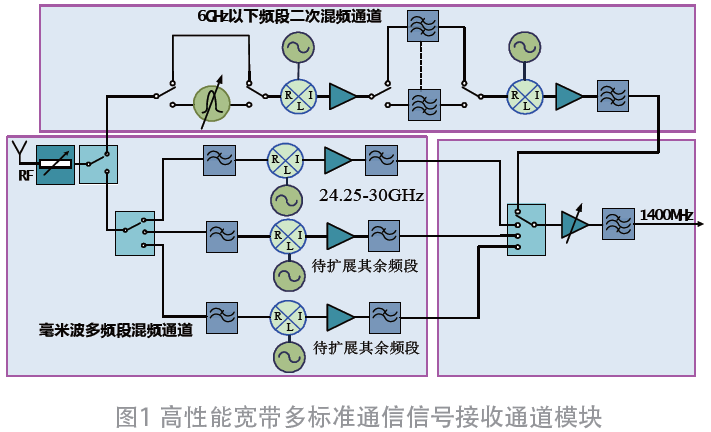

高速多通道信號模擬器采用通用CPC I底板與功能背板相結合的設計思路, 其組成如圖1所示。

高速多通道信號模擬器

圖1 高速多通道信號模擬器

采用上圖所示設計方法, 系統可擴展性強, 不同應用場合只需更換不同的功能背板即可。

2. 2 系統功能

對本文所設計的高速多通道雷達信號模擬器,由FPGA 控制時鐘管理模塊, 為四路DAC5687背板提供相參工作時鐘。同時, 利用X ilinx FPGA 提供的DDS核( IP core)產生信號的樣點數據, 通過高速接插件將信號樣點數據傳輸到DAC5687背板, 在背板上實現數模轉換和信號輸出功能。

3 DAC5687功能背板電路設計

根據DAC5687的工作手冊, 結合圖1中的功能設計, 由FPGA 產生的A、B 兩路信號數據分別通過兩路16bit數據總線傳輸到DAC5687, LVPECL時鐘信號可以選擇與CLK1 /CLK1C 或者CLK2 /CLK2C相連接, 具體由DAC5687的時鐘工作模式決定。當DAC5687工作在內部時鐘模式下, 與CLK1 /CLK1C連接; 工作在外部時鐘模式下, 與CLK2 /CLK2C 連接。另外, NB4N855S是一款電平轉換芯片 , 能將任何電平的信號轉換成為LVDS信號, 本設計中利用這款芯片將DAC5687內部鎖相環PLL 產生的時鐘單端信號轉換成為LVDS 信號, 通過高速接插件傳回通用底板, 作為外部時鐘工作模式下的數據產生同步時鐘。

評論