基于NCOIPcore的Chirp函數實現設計

本文引用地址:http://www.j9360.com/article/187614.htm

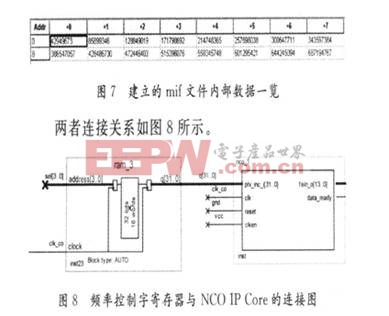

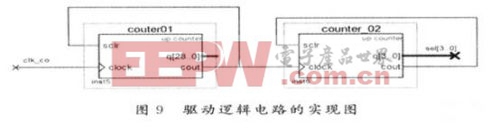

本文引用地址:http://www.j9360.com/article/187614.htm在設計中,通過不同時間點向頻率控制字寄存器寫入不同的地址信號驅動,使存儲器輸出不同的頻率控制字驅動NCO IP Core,產生不同的頻率信號輸出。該設計中采用兩個計數器級聯作為驅動單元,首先第一級計數器將鐘頻率降至需要的Chirp函數輸出某頻點的穩定時間范圍,將第一級計數器的進位端作為第二級計數器的時鐘輸入端;第二級計數器的作用是,產生地址信號以驅動頻率控制字存儲器輸出相應的控制字,當前級進位信號有效時該計數器輸出加“1”。以達到改變頻率輸出的目的,其連接電路圖如圖9所示。

4 仿真與驗證

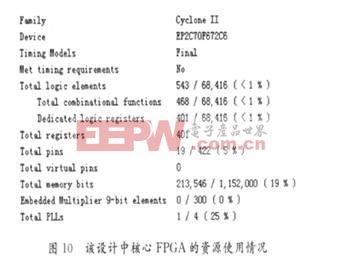

將該設計通過將程序下載到Altera公司生產的DSP開發板(型號DK-DSP-2C70N)中進行仿真,其核心FPGA(型號為EP2C70F672C6)的資源使用情況如圖10所示。

并通過該開發板上D/A轉換器輸出模擬波形(只截取了4個時刻的圖樣)如圖11所示。

通過圖11可以看出該設計能很好地完成掃頻輸出的功能,并且雜波分量很小,干擾很小。

5 結 語

該設計通過采用技術成熟的NCO IP Core完成,其優勢在于:

(1)利用了成熟的FPGA知識產權技術,使得設計更加簡便并易于移植;

(2)利用NCO IP core的高穩定性,使得Chirp函數的各項噪聲較之于其他設計更小,有利于對射電天文這樣微弱信號的處理,減少了處理帶來的各種噪聲。

評論