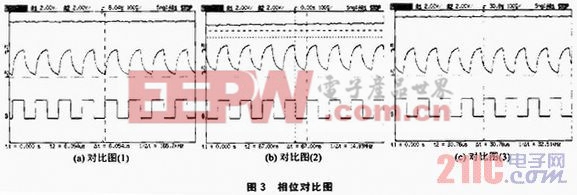

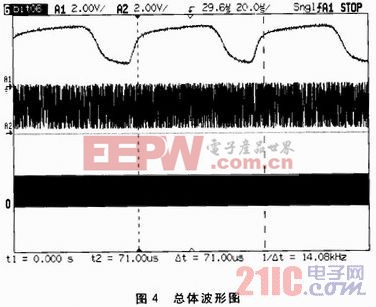

圖2為晶振的模擬通道和數字通道的對比圖。圖3為在頻率合成圖幅值是 之間硅振蕩器和晶振的相位對比圖。圖4為總體波形圖,包括頻率合成圖、硅振蕩器輸出圖和晶振的邏輯分析輸出圖。

之間硅振蕩器和晶振的相位對比圖。圖4為總體波形圖,包括頻率合成圖、硅振蕩器輸出圖和晶振的邏輯分析輸出圖。

從圖3中可以清晰地看出,在范圍之內相位差是比較小的,上升沿的轉換是可以一致的。而在范圍之外相位差就比較大了,上升沿與下降沿相對應,轉換會有跳變,不能實現平穩轉換。通過平穩轉換電路實現的轉換跳變不明顯,示波器上沒有明顯的跳變反應。

4 結論

通過實驗得出的波形與理論相符,在平穩轉換條件下能夠實現穩定轉換,這為下一步在高加速度條件下實現時鐘的精度校準提供了可行依據,也為其他的諸如單片機芯片不同頻率下的轉換提供了實驗依據和簡易方法。

評論