SOPC設計中的兩種片上總線分析

SoC(Systemon Chip,片上系統)以其能提高產品性能、縮小產品體積等優點,逐漸成為嵌入式系統發展的主流趨勢。SOPC(System On a Programmable Chip,可編程片上系統)利用可編程邏輯器件來實現SoC,具有設計方式靈活,可裁減、可擴充、可升級,并具備軟硬件在系統可配置的性能。將處理器IP(Intellectual Property,知識產權)內核嵌入到可編程邏輯器件是SOPC設計的前提條件。

在Altera的FPGA器件上嵌入處理器等IP核可實現SOPC,設計時可使用的RISC處理器核有3種:ARM的工業標準處理器硬核ARM922T、Altera的16位Nios和32位Nios II處理器軟核,而片上總線可采用AMBA和Avalon兩種總線。在嵌入了ARM922T的Excalibur系列FPGA上,使用了AMBA總線的高性能總線AHB(Advanced High-performance Bus);而在可嵌入Nios的FPGA上則使用Avalon總線。這兩種總線也是目前SoC設計使用較多的片上總線標準。

1 片上總線與傳統總線體系的比較

片上總線是實現SoC中IP核連接最常見的技術手段,它以總線方式實現IP核之間的數據通信。片上總線規范一般需要定義各個模塊之間初始化、仲裁、請求傳輸、響應、發送接收等過程中的驅動、時序、策略等關系。

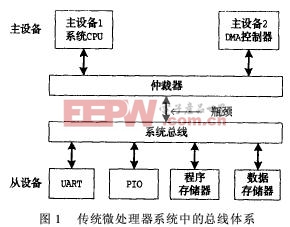

傳統總線協議中,仲裁器控制一至多個總線主設備與從設備的通信。總線主設備首先通過仲裁器來申請總線控制權,然后仲裁器才允許單一主設備訪問總線。如果多個主設備試圖同時訪問總線,仲裁器將根據既定的仲裁策略,將總線資源分配給其中一個主設備。例如,在優先級仲裁機制中,優先級高的主設備將首先得到總線控制權。

控制總線的主設備會占用總線,并與相應從設備通信。圖1說明了優先級仲裁總線體系的結構,該體系在傳統微處理器系統中工作良好。由于主、從設備是位于印制板或底板上的獨立部件,總線需要驅動底板上的信號和連接器。而且,鑒于有限的印制板資源和可用I/O引腳數目,所有系統部件還必須共用總線。

片上總線無需驅動底板上的信號和連接器,使用更簡單且速度更快;同時,為了滿足帶寬要求,片上總線普遍采用并發多主設備總線體系。這種總線體系通過消除傳統總線系統中一次僅有一個主設備可以訪問系統總線的帶寬瓶頸,來增加系統帶寬。在此體系中,總線主設備競爭的是獨立的從設備,而非總線本身。

2 AMBA總線及其應用

2.1 AMBA總線

AMBA(Advanced Microcontroller Bus Architecture)總線用于高性能嵌入式系統,獨立于處理器和制造工藝技術,增強了各種應用中外設和系統宏單元的可重用性。AMBA是多總線體系,目前的AMBA總線規范2.0版定義了3種可以組合使用的總線體系:APB(Advanced Peripheral Bus),ASB(Advanced System Bus),AHB。AHB是現階段AMBA的主要形式。

評論