基于OrCAD/PSpice的晶體振蕩電路設計仿真

3 改進型石英晶體振蕩電路

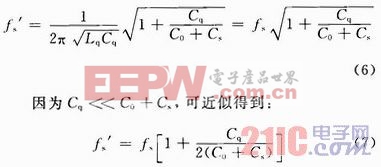

為增加石英晶體振蕩電路的實用性,外接一可調小電容Cs作為微調電容,用于校正振蕩頻率,Cs應比Cq大。接入Cs得到新的串聯諧振頻率:

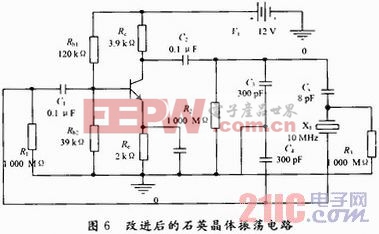

串入Cs后并不影響并聯諧振頻率,當Cs→0時,fs’=fp;當Cs→∞時,fs’=fs;實際使用中用Cs作為微調電容,可使fs’在fs和fp之間的一個小范圍內調整。在仿真調試中發現C5=8 pF時可輸出良好的波形,電路和波形如圖6所示。本文引用地址:http://www.j9360.com/article/185632.htm

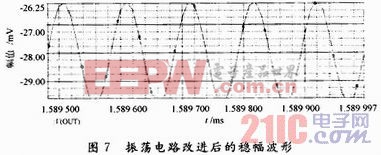

由圖7分析可知:振蕩波形很穩定,振蕩周期為T=1.633 425-1.633 325=0.000 1 ms,f0=1/T≈10 MHz,與無Cs基本一致。

4 結語

本文在電容三點式振蕩電路基礎上設計并改進了石英晶體振蕩電路;通過OrCAD/Pspice仿真分析,以圖像可視化方式顯示了電路起振過程及輸出波形,并通過仿真驗證,電路輸出波形好,諧波分量小。基于PSpice電路仿真設計快捷、直觀,避免了傳統設計方法為確定元件參數進行的復雜運算。

評論