基于全耗盡平面晶體管技術的NovaThor平臺設計

因此,在寬Vdd電壓范圍(0.5V 至 1.3V)內,FD-SOI的綜合性能高于移動處理器專用的體效應CMOS工藝,這些性能優勢可用于提高峰值性能,或者在保證性能不變的前提下降低Vdd工作電壓,從而降低動態功耗。

我們探討了FD-SOI工藝在性能-電壓比方面的技術優勢,接下來,我們將分析另外兩大優勢:具有競爭力的處理速度/泄漏電流比和優化能效。

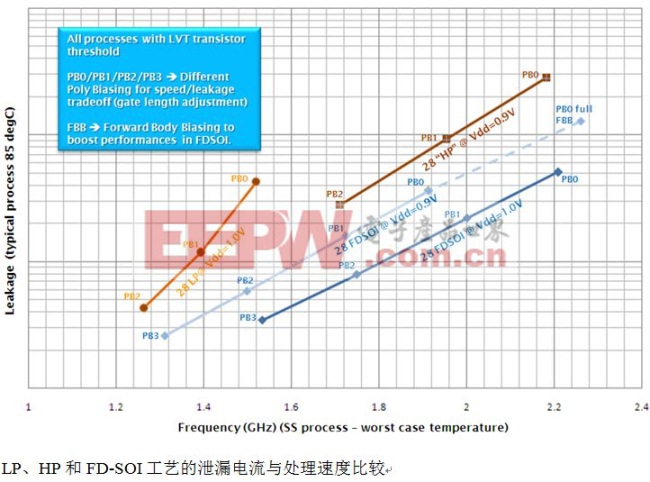

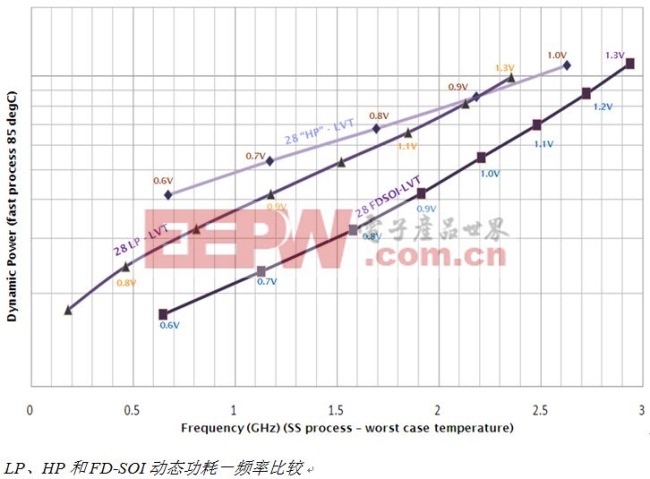

具有競爭力的處理速度/泄漏電流比 FD-SOI工藝不僅帶來前文所述的性能優勢,還具有同級產品最低的泄漏電流,下圖示是前文圖示的ARM Cortex-A9 關鍵通道在85°C時典型泄漏電流與最高頻率之比。以系統的方法分析,當泄漏電流相同時,FD-SOI在標稱電壓(1.0V)時的運行頻率高于標稱電壓(1.0V)時的LP工藝或標稱電壓(0.9V)時的HP工藝。 淺藍色曲線代表Vdd=0.9V條件下的FD-SOI 泄漏電流/速度曲線,這意味著FD-SOI可讓我們降低標稱 Vdd 電壓(對動態功耗影響巨大的參數),同時保持與LP和HP工藝相同的或更高的性能。然后,如藍色延長虛線所示,施加在LVT FD-SOI晶體管上的正向體偏壓(*) 使其能夠達到HP可達到的性能,而在施加偏壓后,多晶硅晶體管的泄漏電流增幅與LP工藝相同。 該泄漏電流/速度比優勢是28nm FD-SOI工藝獨有優勢,真正地融LP 和 HP兩大工藝的優點于一身。 體偏壓是在CMOS晶體管的體效應部分施加可變電壓,以提高泄漏電流為代價換取更快運行速度(正向體偏壓),或者以犧牲性能為代價換取更低的泄漏電流(反向體偏壓)。雖然體效應CMOS具有這項功能,但是,因為埋溝氧化層將晶體管溝道與硅體效應部分(背柵效應)隔離,體偏壓的效果在FD-SOI技術上更加出色。 優化能效 對高端移動應用來說,良好處理性能兼出色的泄漏電流還不夠,在移動設備日常使用過程中降低不同工作模式的總功耗才是最大化電池續航能力的關鍵。 下圖描述了三種不同的 28nm 工藝的動態功耗特性,并給出了動態功耗-最大頻率特性曲線。 從圖中不難看出,在給定頻率時,FD-SOI的總功耗總是比其它兩項技術低很多,即便達到目標頻率所需的電源電壓略高于28nm HP.這主要因為FD-SOI技術的總功耗中泄漏電流較低。在整個電源電壓范圍和對應的性能范圍內均是如此,這充分證明,FD-SOI是能夠給移動設備帶來最高能效的解決方案。 從上文可以看出,28nm FD-SOI在對于移動計算設備極其重要的關鍵參數方面優于現有的體效應工藝,具有高性能且低功耗的優點。

評論