80C51單片機上電復位和復位延時的時序分析

由于標準80C51的復位邏輯相對簡單,復位源只有RST一個(相對新型單片機來說,復位源比較單一),因此各種原因所導致的復位活動以及復位狀態的進入,都要依靠在外接引腳RST上施加一定時間寬度的高電平信號來實現。

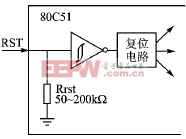

標準80C51不僅復位源比較單一,而且還沒有設計內部上電復位的延時功能,因此必須借助于外接阻容支路來增加延時環節,如圖3(a)所示。其實,外接電阻R還是可以省略的,理由是一些CMOS單片機芯片內部存在一個現成的下拉電阻Rrst。例如,AT89系列的Rrst阻值約為50~200 kΩ;P89V51Rx2系列的Rrst阻值約為40~225 kΩ,如圖4所示。因此,在圖3(a)基礎上,上電復位延時電路還可以精簡為圖3(b)所示的簡化電路(其中電容C的容量也相應減小了)。

圖4 復位引腳RST內部電路

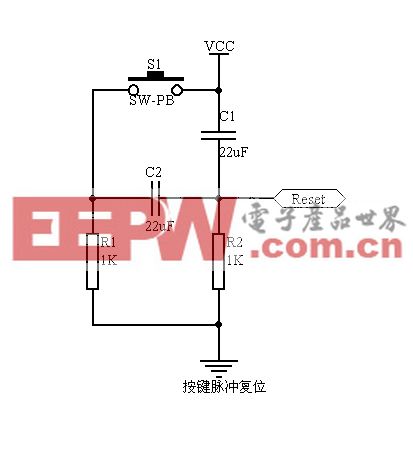

在每次單片機斷電之后,須使延時電容C上的電荷立刻放掉,以便為隨后可能在很短的時間內再次加電作好準備。否則,在斷電后C還沒有充分放電的情況下,如果很快又加電,那么RC支路就失去了它應有的延遲功能。因此,在圖3(a)的基礎上添加一個放電二極管D,上電復位延時電路就變成了如圖3(c)所示的改進電路。也就是說,只有RC支路的充電過程對電路是有用的,放電過程不僅無用,而且會帶來潛在的危害。于是附加一個放電二極管D來大力縮短放電持續時間,以便消除隱患。二極管D只有在單片機斷電的瞬間(即VCC趨近于0 V,可以看作VCC對地短路)正向導通,平時一直處于反偏截止狀態。

3 上電復位失敗的2種案例分析

假如上電復位延遲時間不夠或者根本沒有延時過程,則單片機可能面臨以下2種危險,從而導致CPU開始執行程序時沒有一個良好的初始化,甚至陷入錯亂狀態。

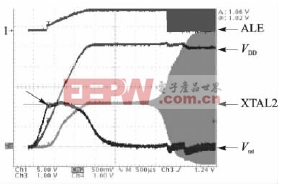

① 在時鐘振蕩器輸出的時鐘脈沖還沒有穩定,甚至還沒有起振之前,就因釋放RST信號的鎖定狀態而放縱CPU開始執行程序。這將會導致程序計數器PC中首次抓取的地址碼很可能是0000H之外的隨機值,進而引導CPU陷入混亂狀態。參考圖5所示的實測信號曲線。

圖5 在時鐘未穩定前釋放RST的情況

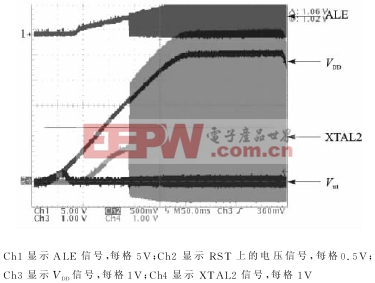

② 在電源電壓還沒有上升到合適范圍之前(自然也是時鐘尚未穩定之前),就釋放RST信號的鎖定狀態,將會使單片機永遠感受不到復位信號、經歷不到復位過程、包含PC在內的各個SFR內容沒有被初始化而保留了隨機值,從而導致CPU從一個隨機地址開始執行程序,進而也陷入混亂狀態。參考圖6所示的實測信號曲線。

圖6 在電源和時鐘均未穩定前釋放RST的情況

評論