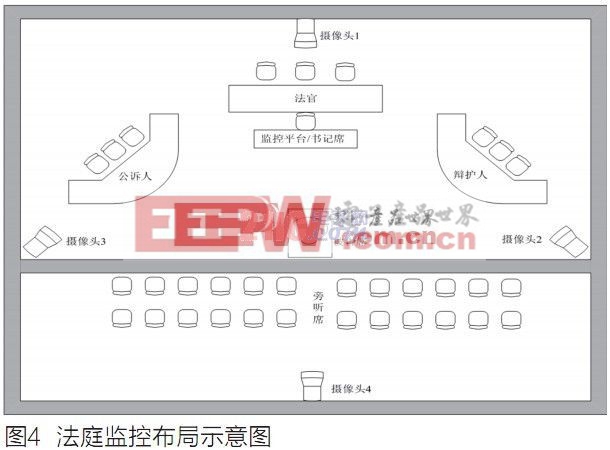

基于TMS320 DM642的多路視頻處理

視頻通路模塊

本設計中將DM642的3個視頻端口VP0VP1VP2均設置為8-bit BT.656模式,其中VP0和VP1采用單通道方式,將通道A用于視頻采集;VP2采用雙通道方式,通道A和B均用于視頻采集。因此,最多可以同時采集4路模擬視頻信號。在BT.656視頻捕獲模式下,FIFO空間總共為2560KB且如下分配:1個1280Byte的FIFO專用于存儲Y采樣數據;2個640Byte的FIFO分別用于存儲Cb和Cr數據。

采用4片飛利浦公司的SAA7113解碼芯片來實現4路模擬視頻輸入的轉換。SAA7113支持6路復合視頻信號CVBS或1路S端子(S-Video)輸入,輸出為帶離散同步信號的8bit4:2:2YCbCr格式或者帶內嵌同步信號的8bitBT.656格式的數字視頻信號。

在視頻回放部分,編碼器選用1片飛利浦公司的SAA7121,其可將數字亮色信號(YUV)或數字RGB信號等數據轉換成CVBS,S-VIDEO,RGB等模擬信號輸出,支持PAL/NTSC制式,并且支持VGA及高清晰HDTV輸出。編解碼器與DM642的引腳連接圖如圖2所示。

DM642中的I2C接口不支持高速模塊,因此在本設計中所使用的I2C總線速率最高為400kbit/s。本設計中采用了TI的4bit 2選1切換器SN74CBT3257使DM642可以每次選擇接收一組I2C數據。由于SAA7113只能配置兩個不同的設備地址,一條I2C總線中不能同時連接4個SAA7113,因此須將I2C總線切分成IIC0和IIC1。具體連接方式見圖3。

軟件設計

設置DM642內部模塊的配置參數,包括VPort視頻端口參數配置,SDRAM及FLASH寄存器配置;I2C總線參數配置;編解碼芯片內部寄存器配置等。

系統上電初始化,DM642通過內部軟件模擬I2C總線時序,配置好SAA7113內部寄存器,設置其工作方式;之后DM642向CPLD發送采集指令,雙方通過HOLD、HOLDA握手信號,實現總線控制交接,此時CPLD獲得總線控制權,然后打開SAA7113的輸出,對采集到的視頻數據進行寫控制;當一幀視頻數據寫入SDRAM幀緩存器后,CPLD關閉SAA7113視頻輸出,放棄總線控制權,并發送中斷信號給DM642;DM642重新獲得控制權后,對采集到的視頻數據使用特定算法進行圖像處理,并將處理后的視頻數據緩存在SDRAM中,同時配置SAA7121內部寄存器,設置其工作方式,此時將SDRAM中緩存的圖像數據送入SAA7121進行D/A轉換,并經過并口送VGA顯示器進行圖像顯示;DM642在圖像處理完畢后即重新發出開始采集命令,進行下一幀數據的采集。

評論