LVDS技術在數字視頻傳輸系統中的應用

1.2.1 串行/解串器

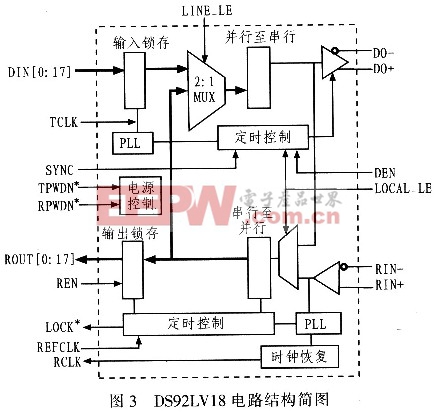

串行器和解串器采用18位高性能串行/解串器DS92LV18,其主要性能特點:時鐘頻率15~66 MHz,可支持0.27~1.188 Gb/s的有效載荷;收發一體設計,內置發射/接收數字鎖相環,提供幀同步、幀檢測、時鐘恢復功能;具有“即插即用”的同步操作能力,帶電插接時無需系統干預。DS92LV18在系統的發送單元中主要是將數字圖像數據、時鐘和同步等信號由并行轉為串行的LVDS信號,在接收單元中主要將串行的LVDS信號數據解串恢復成并行的圖像數據、時鐘和同步信號。圖3為DS92LVl8的結構簡圖。

DS92LVl8的引腳配置如下:

DIN[0:17]:18位并行LVTTL/LVCOMS輸入數據信號;

TCLK:編碼時鐘,當編碼器工作時,該時鐘信號經編碼鎖相環20倍頻后將DIN[0:17]和TCLK編碼成20位串行數據信號,以LVDS標準電平信號從D0+和DO-輸出,應用中要求與解碼時鐘REFCLK同頻率,2個時鐘頻率偏差不能超過5%;

SYNC:編碼器工作控制信號,當編碼器和解碼器工作時,置低電平;

TPWDN、DEN:編碼器工作控制信號,當編碼器工作時,置高電平;當解碼器工作時,置低電平;

RPWDN、REN:解碼器工作控制信號,當解碼器工作時,置高電平:當編碼器工作時,置低電平;

RIN+、RIN-:解碼器輸入串行LVDS信號;

評論