基于STD總線的多路數字I/O設計

3.1 部分程序代碼

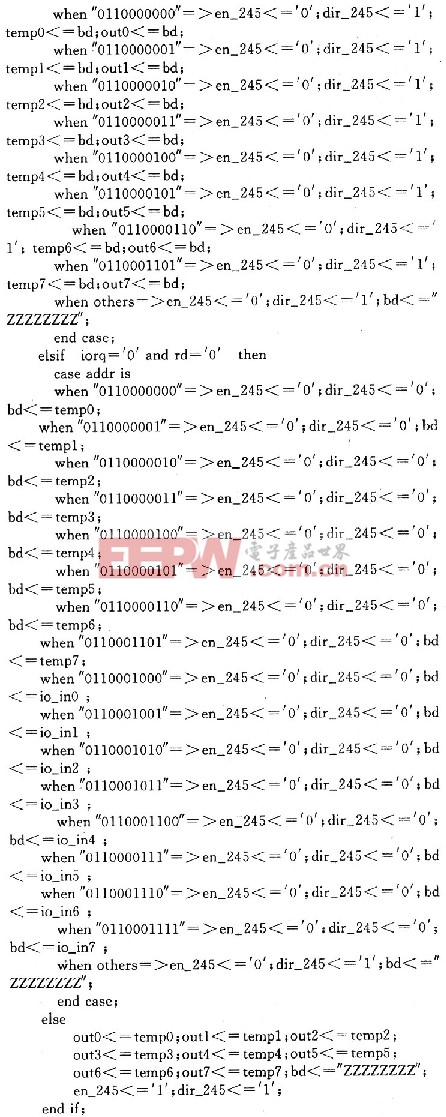

部分程序代碼如下:

其中:addr是10位地址總線;bd是8位數據總線;en_245和dir_245分別是STD總線接口芯片74LS245的片選使能與方向信號;tempx是片內寄存器;io_inx和outx分別是8位輸入、8位輸出I/O口。

3.2 性能描述

多路數字I/O口的選擇由10位地址決定,不同的地址操作不同的。I/O端口,在I/O非動態情況下,數據總線處于高阻狀態,避免了總線沖突,同時也提高了I/O端口的穩定性,減少了高速數據傳輸條件下引起不必要的錯誤,根據現場對I/O輸入、輸出的需要,可以修改程序,靈活改變端口的功能,另外,對于輸出端口,加入了數據寫出后讀回的功能,使得上位機能夠隨時驗證寫出數據的正確性,對于外設信號,通過信號調理板實現電平匹配,進一步增加了本設計的功能可靠性。

4 結語

以CPLD器件為核心,選用Xilinx公司的ISE作為硬件開發平臺,并采用VHDL編程語言,充分應用了可編程邏輯器件的特點,發揮了VHDL硬件描述語言的編程優點。減少了芯片數量,既做到了系統小型化又降低了成本。程序已通過綜合實驗,應用了STD總線的通訊特點,與總線上的其他板卡、設備通訊也極為方便,既解決了工業通信網絡的一般問題,又達到了工業通用I/O的較高要求。總之,該多路數字I/O設計容量高、功耗低、速度快,不僅具有通用性、實用性,而且具有靈活性和移植性,便于調試,為高速I/O開發設計提供了一種很好的嘗試,相信在很多行業都會有廣闊的應用前景。本文引用地址:http://www.j9360.com/article/162940.htm

評論