基于絕對編碼器的數據采集

3 接口的設計及編程

編碼器要求時鐘發生電路提供的時鐘信號可以調整,調整范圍為100 kHz~1 MHz。根據邏輯時序的要求,在靜止條件下,時鐘和數據信號處于邏輯高電平上,編碼器內部單穩態電路不工作。在第一個時鐘信號下降沿,單穩態電路啟動,編碼器內部的并行數據信號輸入到P/S(并/串)轉換器,并在轉換器內存儲。在時鐘信號上升沿MSB(最高有效位)被傳送至輸出端的數據線上。當時鐘信號再次至下降沿,接口從數據線上得到MSB數據,當數據穩定后,單穩態電路再次重新啟動。每次當順序時鐘脈沖信號在上升沿時,數據連續傳送至輸出數據線上,同時需要控制信號處于下降沿。在順序時鐘脈沖結束時,外部控制信號時鐘需要獲得LSB(最低有效位)的數據,當順序時鐘脈沖被中斷,單穩態電路不再啟動。一旦TM(單位定時電路時間信號)消失,數據線路回到邏輯高電平上,編碼器內部單穩態電路自動停止工作。信號波形示意如圖2所示。本文引用地址:http://www.j9360.com/article/162261.htm

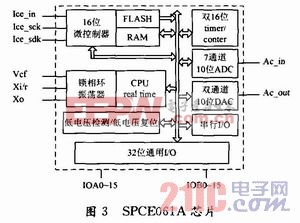

為了產生時鐘信號,選用SPCE061A芯片作為處理器,該芯片為16位芯片,帶32位I/O,具有串行輸出接口,雙16位定時器/計數器,內部結構如圖3所示。

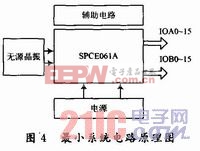

以SPCE061A芯片為處理器,設計一個最小系統,如圖4所示。

評論