ISE入門三部曲

此時我們可以查看RTL級的原理圖,雙擊 View RTL Schematic,并選擇Start With a schematic of the top-level block,點擊OK如圖13所示,然后將出現一個模塊,上面有我們寫的輸入輸出。

本文引用地址:http://www.j9360.com/article/159138.htm

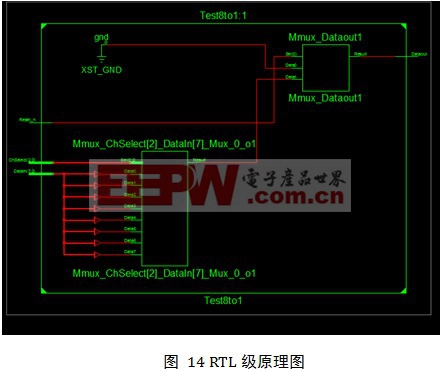

雙擊模塊,將出現如圖14所示的原理圖,查看原理圖,可以查看原理圖是否與自己的設計一致,利于檢查連線錯誤等。如果邏輯比較簡單,查看原理圖即可知道設計的目標是否達到,例如本例中的8路選擇器,從綜合生成的原理圖可以看出,正常情況(Reset_n信號無效)是一個8路選擇器,復位時輸出為零;當邏輯比較復雜時,原理圖龐大,無法仔細去比對是否達到自己的目的,此時就需要進行軟件仿真。

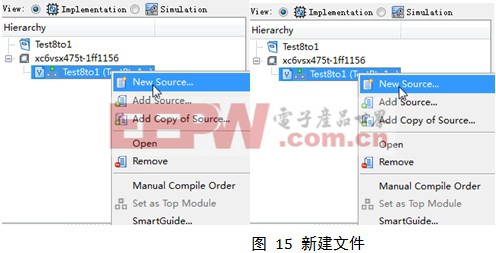

那么我們首先編寫TestBench程序,點擊菜單欄的Project(或者右鍵單擊到工程的文件),NewSource 選擇 Verilog Test Fixture,輸入文件名TestModule ,點擊Next,選擇要關聯的源文件,這里只有一個源文件 Test8to1,如果有多個源文件,則需選擇對應的需要仿真的文件,然后點擊Next。

可控硅相關文章:可控硅工作原理

比較器相關文章:比較器工作原理

評論