FPGA設計經驗談

5)關于IP核和乒乓操作的那點事

本文引用地址:http://www.j9360.com/article/158978.htm經驗告訴我,能使用開發工具自帶的IP核,就千萬別去自己開發。往往自己開發已有的IP核是吃力不討好。我曾經做過一個eMMC控制器燒寫外部eMMC芯片的案子。

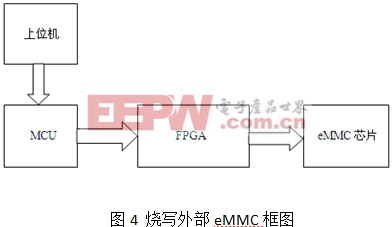

數據由上位機通過USB傳給MCU,然后通過數據總線發到FPGA,在FPGA內部形成燒寫eMMC芯片的時序,燒寫外部芯片。框圖如下:

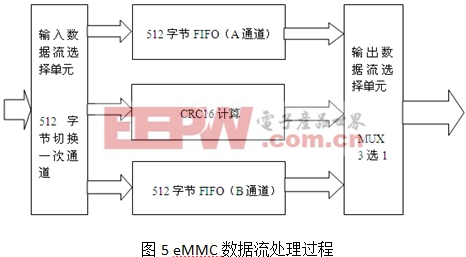

最初的算法是通過數據總線發一個字節,再向芯片打一個字節,一個頁的512字節的CRC16需要事先用軟件計算好,但是這種方式燒寫速度太慢。后來我想到一種方案,先把512個字節傳到FPGA內部存儲起來,并且在FPGA內部計算好16個字節的CRC,然后用高速系統時鐘一次性把整頁528個字節傳給芯片,這種方式燒寫速度能提高很多。一開始我想自己設計一個帶CRC計算的RAM或者FIFO來存儲528個字節的數據,可是無論怎么設計數據傳輸總是有問題,由于是一個人做,也沒人指導,只得放棄這種方案,改用其他。因為我用的Xilinx器件有現成的FIFO核可以調用,于是我就把CRC16的計算和存儲512字節數據分開設計,在最后輸出到芯片端再選通。因為燒寫eMMC一個頁,需要有一定的等待POLLING時間,所以我想到了用兩組FIFO,乒乓操作,A通道數據發送到芯片并且等待應答的時候,MCU端向B通道發送數據存儲,B通道數據發送到芯片并且等待應答的時候,MCU端再向A通道發送數據存儲,這樣最大化的加速了燒寫速度,當然最后的設計結果我也是相當滿意的。

我想通過此例告訴大家的是,盡量用系統的IP核吧,省事又省心,因為這些都是前輩專家們設計出的經典。還有就是利用一些設計技巧,比如乒乓操作,流水線操作可以讓你的設計性能優化不少。

最后簡單說一下體會吧,歸結起來就多實踐、多思考、多問。實踐出真知,看100遍別人的方案不如自己去實踐一下。實踐的動力一方面來自興趣,一方面來自壓力,我個人覺得后者更重要。有需求會容易形成壓力,也就是說最好能在實際的項目開發中鍛煉,而不是為了學習而學習。在實踐的過程中要多思考,多想想問題出現的原因,問題解決后要多問幾個為什么,這也是經驗積累的過程,如果有寫項目日志的習慣更好,把問題及原因、解決的辦法都寫進去。最后還要多問,遇到問題思索后還得不到解決就要問了,畢竟個人的力量是有限的,問同學同事,問搜索引擎,問網友,都可以,一篇文章、朋友們的點撥都可能幫助自己快速解決問題。

逆變器相關文章:逆變器原理

fpga相關文章:fpga是什么

可控硅相關文章:可控硅工作原理

pwm相關文章:pwm是什么

c語言相關文章:c語言教程

逆變器相關文章:逆變器工作原理

比較器相關文章:比較器工作原理

評論