基于FPSLIC的UHF頻段RFID閱讀器的實現

通常,RFID系統由電子標簽(tag)、閱讀器(reader)和數據管理系統這三個主要部分組成,如圖1所示。

電子標簽部分又可以細分為標簽天線和標簽芯片兩部分。每個電子標簽都含有唯一的識別碼,用來表示電子標簽所附著的物體。當電子標簽接收到閱讀器的發射信號的時候,電子標簽被喚醒,然后根據閱讀器發射的指令完成相應的動作,并將響應信息發射回給閱讀器。電子標簽上有數KB的存儲單元,可以反復讀寫10,000次以上。

閱讀器也可以細分為閱讀器天線和閱讀器兩部分。閱讀器通過發射信號喚醒和傳送指令給電子標簽,并接收標簽返回的信號。在初步的過濾、處理信號之后,將有用的數據通過網絡和數據管理系統交互,從而完成對電子標簽的信息獲取和解析。

數據管理系統主要完成數據信息的存儲及管理、數據管理系統可以由簡單的小型數據庫擔當,也可以是集成了RFID管理模塊的大型ERP數據庫管理軟件。它通過網絡與分散在異地的閱讀器通信,實時獲取閱讀器捕獲到的電子標簽信息。

按頻段RFID產品可以分為低頻125KHz、高頻13.56MHz、超高頻915MHz以及微波頻段2.45GHz和5.8GHz。本文實現了具有自主知識產權的UHF頻段(915MHz)RFID閱讀器。UHF閱讀器兼容識別ISO18000-6和ANSI256的無源RFID標簽,可根據發射功率調整識別距離。閱讀器識別無源RFID標簽可達5~10米的識別距離,50張標簽/秒,并采用了RFID信號防沖撞算法,可以同時識別同一區域內多張RFID標簽。

圖2主控板框圖

本設計方案可以廣泛應用在以下領域:

1.制造業,實現精細制造,提高生產效率,保障產品質量。

2.企業供應鏈管理,有效控制企業庫存量,降低市場風險,提高盤點效率。

3.倉儲物流業和交通運輸,物流全過程的跟蹤監控,提高調度的準確性和效率。

FPSLIC就是在基于SRAM的SoC中嵌入AVR MCU內核和FPGA門陣列邏輯。AVR、FPGA、SRAM模塊之間的接口已經實現,而且可以配置,可以節省2000~5000門。一個FPSLIC里有10000~ 40000門的FPGA、一個單片機、一個儲存器、多種外圍設備和現成的接口。其低價格的軟件包括:設計主控流程、綜合驗證、布線工具以及硬件和軟件的仿真。

嵌入在FPSLIC 里的MCU為Atmel的AVR。它是一個8Bit RISC的MCU,可以執行的單時鐘指令可達120多條,AVR代碼效率和性能跟一般8位的MCU相比凸顯優越。當把它嵌入以SRAM為主的FPSLIC時,更可表現其三大特點 :提高速度、降低功耗、程序存儲量降低。

嵌入在FPSLIC 中的FPGA為Atmel的AT40K系列。該系列FPGA內有10ns的分布式SRAM,它可以異步操作,也可以同步操作。AT40K的設計是用VHDL/Verilog或畫圖的方式在計算機上形成的。由于AT40K還可以當作DSP的協處理器使用。客戶可以把一些需要快速執行的功能在FPGA里實現,比如FIR、FFT、interpolators 和DCT,從而使得該FPGA能很好地應用在多媒體、電信和工業控制等領域。

AT94K40的內部程序/數據SDRAM分為3塊:10K16位專用程序存儲器(地址范圍:0x0000~0x27ff);4K8位專用數據存儲器(0x0000~0x0fff);6K16位或12K8位可配置存儲器。

開發軟件采用System Designer 3.0。硬件和軟件同步仿真。

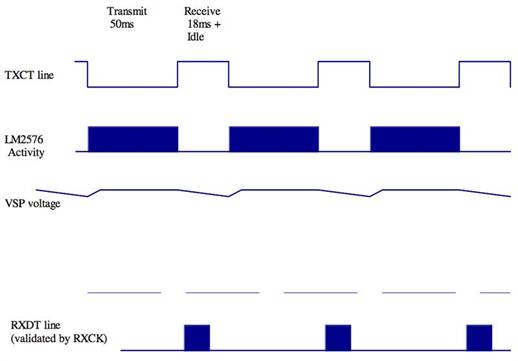

本設計的主控板框圖如圖2所示。

本方案的具體設置包括:

1.現在使用的設置為16K16位的程序存儲器,4K8位的數據存儲器。在4K8位專用數據存儲器(0x0000~0x0fff)中包含了64個AVR I/O寄存器。其中AVR與FPGA的通信中使用到了以下寄存器:

FISCR:FPGA I/O選擇控制寄存器

FISUA~D:FPGA I/O選擇、中斷控制寄存器

2. 考慮到需要以80KHz頻率發送OOK信號,通常的4MHz的板上晶振在不分頻的情況下使用匹配中斷(匹配值為50),才勉強實現,但由于指令執行周期(0.25s)太長,實際發送OOK信號時達不到要求的速度。故改用18.432MHz的晶振,匹配值為225。匹配值的計算公式為:匹配值=晶振頻率/分頻系數/80KHz。

3. AVR代碼中使用了Uart01的接收/發送中斷與Timer0的匹配中斷。

4. 波特率設置:BAUD=Fck/16*(UBR+1),Fck為時鐘頻率,UBR為波特率寄存器高字節UBRHI和低字節UBRRn的數值(0~4095)。下面給出典型值:

Fck=4MHz,UBR=25,BAUD= 9600bps

Fck=18.432MHz,UBR=9,BAUD= 115200bps

5. 由FPGA實現的功能為:補碼變換,差分處理,FIR低通濾波,歸一化判決,去毛刺,同步提取。

其中對各步驟簡要說明如下:

a)補碼變換:因為ADC的輸出信號為1ff~000(3~2V), 3ff~200(2~1V)。若要分出信號的正負,就需要本步驟,具體操作為將大于511的輸出減去1024。

b)差分處理:增強信號。

c)FIR低通濾波:去除高頻噪聲。

d)歸一化判決:將A/D采樣得到的電壓值轉變為I/O信號。

e)去毛刺:去除毛刺信號。

f)同步提取:提取碼元信號,平均一個碼元擁有4個采樣點。

采用FPSLIC開發優勢在于:資源比較豐富,I/O設置很靈活,有很大的發揮余地;FPGA的運算速度很快;由于使軟硬件同步仿真,雖然難度大了,但也縮短了開發周期;總體的性價比好。

感覺不足的地方有:AVR協同FPGA工作的速度跟不上,當運作頻繁時總是FPGA等候AVR;System Designer的界面不夠友好,使用起來不太方便;布線的速度慢。

總體來說,本文利用FPSLIC實現了超高頻段RFID閱讀器,為 FPSLIC在這方面的應用打開了思路。

評論