數字差分BPSK擴頻接收機的設計與FPGA實現

關鍵字:FPGA,擴頻,同步

1引言

隨著軟件無線電技術的發展,傳統的基于復雜模擬硬件的接收設備逐漸向數字IC產品過渡,而FPGA作為ASIC產品原型設計的可編程邏輯器件,以其豐富的邏輯資源和可重新配置的優勢,成為人們前期研究與開發的重要手段。因此,在可編程邏輯器件上實現數字擴頻接收機關鍵技術進行研究,具有重要的應用價值。

本文給出了一種數字差分BPSK直接序列擴頻接收機的方案,并通過simulink進行了仿真,同時本文深入探討了方案中的關鍵技術在FPGA中的實現結構,在保證系統穩定性,和不影響系統性能的前提下降低硬件復雜度的問題上提出了FPGA實現方案,并最終在Xilinx XC2V500 FPGA上實現了整個系統,對工程實踐有一定的指導意義。

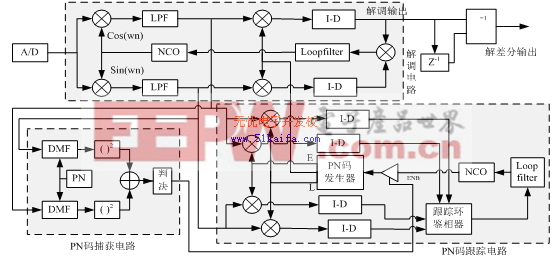

數字BPSK擴頻接收機原理圖見圖1,系統主要可以分為三個部分:解調電路、PN碼捕獲電路和PN碼跟蹤電路。

圖1 數字差分BPSK擴頻接收機原理圖

*本文工作得到國家自然科學基金資助(批準號:60171037) |

通過Simulink仿真該系統,同時結合Xilinx公司FPGA特點,對硬件電路實現進行探討,在保證系統性能的前提下,減小硬件實現復雜度。 下面將具體介紹電路各部分原理與硬件實現。

2.1 數字解調

BPSK信號的解調通常采用相干解調的方式,已經證明跟蹤低信噪比的抑制載波信號的最佳裝置是Costas環及平方環[1],并且這兩種結構是等效的,在數字域中通常采用Costas環實現載波同步。

Costas環電路結構見圖1解調電路,電路各部分實現如下。

(1)數控振蕩器(NCO)

數控振蕩器采用查找表結構,即預先將正弦信號樣本存儲在ROM中,通過相位進行累加,將結果作為ROM地址信號進行查表,得到的輸出即為正弦信號,此處的ROM可由FPGA中的塊RAM實現。

(2)解擴單元

直擴通信中,需要先解擴才能使Costas環正常工作,下變頻后的數據先利用已經同步的PN碼進行解擴處理。解擴過程并不需要乘法器,可以利用異或邏輯完成。本系統實現中將PN碼事先存入FPGA的基本單元-查找表(LUT)中,令LUT實現移位寄存器功能,利用跟蹤單元生成的同步PN碼時鐘進行移位,移位輸出的PN碼與輸入信號進行異或,完成解擴。

(3)積分清零器(I-D)

積分清零器對一個PN碼周期的數據進行累加,輸出與信息碼元相同速率的比特流,完成相關運算,同時起到低通濾波的作用。

(4)環路低通濾波器

乘法鑒相器的輸出經過環路濾波器后,去修正數字控制振蕩器的頻率控制字,完成閉環控制。Costas環采用二階環路,對應一階環路濾波器,濾波器的傳輸方程為[2]:

其中系數C1,C2可以由理論推導得出,實際應用中也經常采用經驗比值 ,具體數值根據實際仿真結果選擇。

,具體數值根據實際仿真結果選擇。

2.2 PN碼捕獲

PN碼捕獲在載波恢復之前。PN碼同步分為捕獲和跟蹤兩個階段:捕獲完成粗同步,使PN碼同步誤差在一個碼元之內;跟蹤完成精確同步,使本地PN碼與輸入序列PN碼精確對準。PN碼捕獲存在多種算法,匹配濾波法具有捕獲時間短的特點,因此本文采用這種方法。

匹配濾波器的原理比較簡單(電路見圖1 PN碼捕獲電路),捕獲過程利用本地PN碼對I、Q兩路同時進行相關處理,然后能量求和后檢測峰值。通常為了降低虛警同步的概率,可以設計同步狀態機,當峰值超過某閾值時,認為PN碼達到預同步,經過一個PN碼周期,再檢測閾值,這樣經過多次檢測,每次都超過閾值時認為捕獲成功,這樣設計可以大大減小PN碼捕獲的虛警概率。

傳統的并行數字匹配濾波器在實現上存在資源占用率大的缺點,本設計中針對FPGA內部特點,采用折疊型匹配濾波器[3]。折疊型濾波器允許使用者更加靈活的從占用芯片資源與芯片處理速度之間做出折衷的選擇,給實際應用帶來了很大的方便。

具體地,系統中的PN碼長為15位,4倍過采樣率,對應折疊型匹配濾波器結構如下圖。

圖2 折疊型匹配濾波器原理圖

如圖2所示,PN碼折疊存放,因為PN碼長15位,所以圖中的第16位碼并不參加運算。每輸入一個數據,濾波器以4倍輸入數據的時鐘頻率進行處理。在第一個時鐘周期,Code 0,Code 1,Code 2,Code 3與輸入數據作相關,并與前一級的SRL輸出相加,此時最左端加法器加0,最后一級SRL的值移至保持寄存器;第二、三個周期操作相同,分別選用接下來的兩組PN碼做相關,最左端的加法器輸入為保持寄存器的數值,最后一級仍移位至保持寄存器;第四個周期前面操作與第二、三周期相同,最后一級的相關值并不參加運算,而是上一級SRL的輸出直接移入本級的SRL,同時本級的SRL輸出至相關輸出寄存器。

其中SRL和存放PN碼的移位寄存器可以用LUT實現,這樣就大大節省了FPGA中相對緊俏的寄存器資源,同時折疊濾波器的處理時鐘需要是輸入數據速率的4倍。數據位寬是影響資源占用的一個重要因素,設計中為了兼顧硬件資源和系統精度,截斷數據位寬為8bit。

2.3 PN碼跟蹤

當捕獲信號的檢測統計量大于預先設定的門限時,跟蹤電路就被開啟。跟蹤的基本方法是利用鎖相環路來調整本地時鐘的相位,常用的跟蹤環路有延遲鎖相環(Delay locked Loop,DLL)及 抖動鎖相環(Tau dither Loop,TDL)。本系統采用延遲鎖相環法。

延遲鎖相環是一種非相干跟蹤環路,如圖1 PN碼跟蹤電路所示,相關原理請查閱參考文獻[4]。

在PN碼捕獲之后,得到了粗同步后的PN碼,然后進入跟蹤環。其中PN碼發生器產生超前和滯后1/2PN碼碼元周期的兩個碼組E和L,分別與I、Q兩路進行相關,之后得到四路相關值記為 此部分電路結構與Costas環中解擴和積分清零相同,不再贅述。

此部分電路結構與Costas環中解擴和積分清零相同,不再贅述。

(1)跟蹤環鑒相器

跟蹤鑒相器存在多種算法[1],本文采用超前減去滯后能量的運算,即

鑒別器輸出=

在 個碼片的輸入誤差范圍內,它跟超前減去滯后包絡的運算有相同的DLL鑒別器誤差性能,卻降低了硬件實現的復雜度。

(2)NCO

碼跟蹤環的NCO結構比較簡單,容易設計,通常采用累加器跟一個固定頻率控制字和來自環路濾波器的誤差控制信號共同構成。其中固定的頻率控制字根據累加器時鐘和PN碼鐘以及累加器所用的位數計算得出,累加器不斷的進行累加,這樣累加寄存器的最高位不斷的產生“0”“1”變化,從而形成一定周期的脈沖,用此脈沖作為PN碼移位寄存器時鐘。NCO累加器輸入端的誤差控制信號,即環路濾波器的輸出,可以改變產生的脈沖頻率,從而使本地PN碼更加精確地對準輸入信號PN碼,完成跟蹤。

NCO的跟蹤精度和累加器的累加時鐘以及累加寄存器大小有關,累加時鐘頻率通常較高,可以采用FPGA中時鐘管理單元DCM對低頻時鐘進行倍頻得到。

3 仿真結果

Simulink仿真所采用的接收機參數如下:

l PN碼長度:15

l PN碼碼片速率:5Mbps

l 載波頻率:10MHz

l 采樣頻率:40MHz

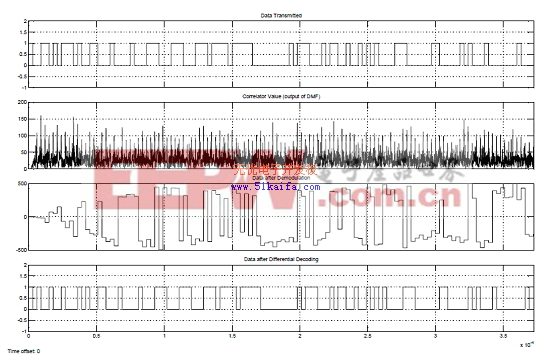

下面給出了在SNR= -5dB,多普勒頻移100Hz的高斯信道下的Simulink仿真結果。為了解決BPSK解調的相位模糊問題,在發送端對信號進行了差分編碼調制,在接收端進行差分譯碼。從最后的差分譯碼的結果可以看出,在經過幾個碼元周期后,信號能夠被正確的解調。仿真結果表明,誤碼率可以達到10-5以下,滿足系統既定要求。

圖3 Simulink仿真結果

4 FPGA實現

實驗用電路板上包括Xilinx公司FPGA XC2V500,AD公司的模數轉換器AD9238,同時板上提供了與TI公司C6000系列評估板的接口。中頻信號經過AD采樣,利用FPGA實現擴頻系統的解擴和解調等功能,通過EMIF接口將數據傳給DSP,進一步完成通信系統中其他應用與設計,整個系統構成軟件無線電通用平臺。

系統采用同步設計方法,時鐘源由電路板上40MHz石英振蕩器提供。XC2V500高達50萬門,其中集成了大量的乘法器,DCM以及全局時鐘布線資源,給系統實現帶來了很大的方便。系統在實現時需要多個時鐘,主要由DCM分頻和倍頻得到。實現中,除了上述對電路進行的優化設計,在不影響系統性能的情況下,對運算的中間結果進行尾數截斷,很大程度提高了硬件資源的利用率。

利用Verilog編程,XST綜合,布局布線后,通過Modelsim后仿真驗證電路的正確性,并最終在FPGA芯片上實現。芯片資源占用如下表,其中使用的Slice占FPGA中Slice總量的14%。

基本單元 | Slice | IO | BRAM | MULT18X18 | GCLK | DCM_ADV |

使用數量 | 451 | 19 | 1 | 9 | 7 | 2 |

5結論

本文作者創新點是提出了一種全數字差分BPSK擴頻接收機的完整方案,并針對Xilinx公司FPGA特點,對系統電路結構進行優化設計,降低了硬件復雜度,實現了高速信號傳輸和低誤碼率的擴頻接收機系統。

本中給出了系統的Simulink仿真結果,以及利用Verilog編程,通過綜合和驗證,在Xilinx XC2C500芯片上實現的結果,對工程實踐有一定的指導意義。文中討論的方法具有通用性,實際應用中可根據具體情況修改電路參數,以適用不同要求。

6參考文獻

[1] 張欣 著. 擴頻通信數字基帶信號處理算法及其VLSI實現. 科學出版社. 2004.8.

[2] Jen-Shi Wu, Ming-Luen Liou, Hsi-Pin Ma, and Tzi-Dar Chiueh. A 2.6-V, 44-MHz all-digital QPSK direct-sequence spread-spectrum transceiver IC. IEEE Journal of solid-state circuits, vol. 32 No.10. October 1997

[3] 卿敏,沈業兵,安建平. 用FPGA實現數字匹配濾波器的優化方法. 微計算機信息. 2004年第20卷第11期.

[4] 鄭繼禹,林基明著. 同步理論與技術. 電子工業出版社. 2003.3

評論