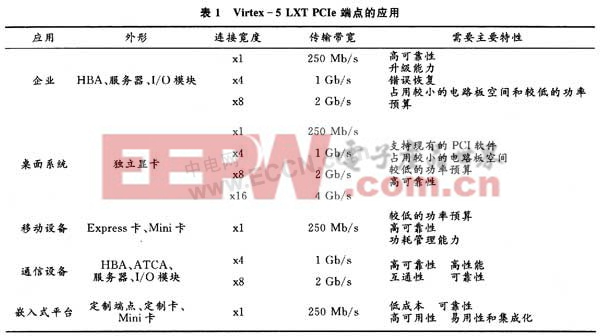

基于Virtex5的PCI Express總線接口設計

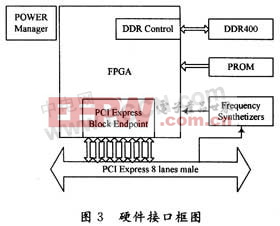

接口硬件主要由主控FPGA模塊,電源管理模塊,DDR高速緩存模塊、和時鐘管理模塊組成。硬件結構框圖如圖3所示。

FPGA是整個設計的最關鍵部分,主要實現:PCI-Express硬核;在硬核的用戶接口和傳輸接口實現PCI-Express傳輸本地總線的時序邏輯;并且在其內部完成DDR控制時序邏輯。FPGA是PCI-Express接口和DDR內存單元數據傳輸的通道。這里選擇XilinxVirtex5系列FPGA中的V5LX50T芯片,封裝形式為FFGll36。

在整個電路中,FPGA的功耗最大,因此在電源模塊設計中,重點考慮FPGA因素。FPGA的功耗與設計有關,主要取決于器件的型號、設計的時鐘頻率、內部設計觸發器翻轉率和整個FPGA的資源利用率。這里使用Xilinx功耗分析工具XPower進行功耗分析,根據XPower提供的動態功耗和靜態功耗分析結果,選擇TI公司的相關電源模塊。

DDR是比較常用的高速緩存單元,這里選擇使用現代公司的HY5DU56822DT-D4,在PCI-Express傳輸過程中,對時鐘的穩定性要求很高;Virtex5 FPGA內部的CMT模塊的時鐘綜合處理能力可能達不到預想的效果,這里使用專門的時鐘管理單元提供時鐘,選擇的是ICS874003芯片,通過FPGA管腳控制其時鐘綜合的效果。

3.2 軟件設計

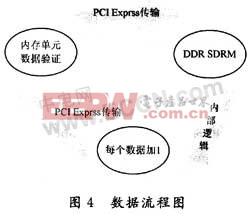

在實現PCI-Express數據傳輸過程中,構建數據傳輸流程如圖4所示。

數據從PC內存通過PCI-Express接口向下傳輸到FPGA內部,FPGA內部DDR控制邏輯再將數據傳輸到的DDR內存芯片中存儲,向下傳輸完畢后,FPGA內部邏輯從DDR芯片中將存儲的數據讀出,并且給每個數據按字節加‘1’,然后通過PCI-Express接口,再將數據傳輸回PC內存,PC內存程序對數據進行校驗。

4 結 語

Virtex5系列FPGA芯片內嵌PCI-Express End-point Block硬核,為實現單片可配置PCI-Express總線解決方案提供了可能。基于Virtex5 FPGA的PCIExpress設計實現方式簡單、配置靈活,適合于各種應用領域,降低了設計成本,縮短了產品上市時間,保證了產品的功能性和易用性,開創了高效率PCI Express開發的新時代。

評論