MT-ZigBee硬件平臺的設計

MC13192的IRQ管腳連接到GB60的IRQ管腳上,MC13192上產生的所有中斷事件直接反映給GB60。當GB60接收到來自MC13192的外部中斷時,還要查詢其中斷標志寄存器,來判斷產生的中斷事件,并作出相應的處理。

在GB60對MC13192的3個控制口中,ATTN管腳用于MCU、將MC13192從低功耗模式下喚醒,而RXTXEN管腳則用來使能MC13192的收發器。在通常情況,為了降低功耗,射頻芯片的收發器都是關閉的,只有在發送和接收數據時才使能有效,這樣能大大降低射頻芯片的功耗。當射頻芯片工作異常時,MCU也可以通過RST管腳來硬件復位MC13192。

MC13192的時鐘輸出引腳CLKO直接與GB60的EXTAL引腳相連接,從而GB60不再需要外部晶振電路的支持,直接采用來自MC13192的時鐘源即可。該時鐘源是可編程的,能夠提供8種不同的時鐘頻率:16 MHz,8 MHz,4 MHz,2 MHz,1 MHz,62.5kHz,32.768 kHz和16.393 kHz。

2.2.3 MC13192無線射頻通信模塊設計

射頻電路的設計是硬件設計中最為復雜的部分。這一部分對PCB的材質、電阻電容的精度、電路的走線等都有很高的要求,其參數選擇的好壞直接影響到射頻電路的質量。

射頻電路的設計是參考Freescale,Microchip等公司給出的參考樣例進行設計開發的。

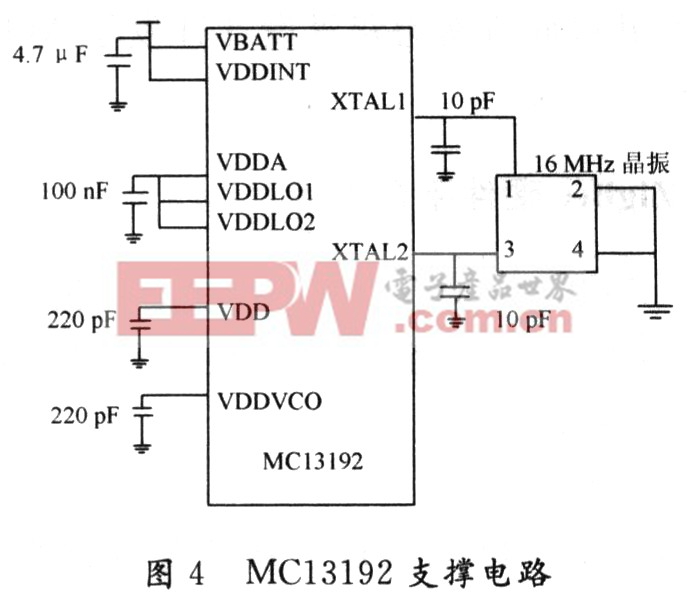

(1)MC13192支撐電路的設計。MC13192的支撐電路包括電源電路,濾波電路和晶振電路,其邏輯連接如圖4所示。VBATT和VDDINT是電源輸入引腳,MC13192的正常工作電壓為2.0~3.6 V,必須接一個4.7μF的穩壓電容。VDDA,VDDL01和VDDL02為經過整流的模擬電壓,必須旁接一個100 nF的濾波電容。VDD為經過內部整流的數字電壓,旁接一個220 pF的濾波電容。VDDVCO為VCO電路供電,同樣必須旁接一個220 pF的電容。XTAL1和XTAL2外接16 MHz的專用于2.4 GHz射頻電路的晶振,其旁路電容為1O pF。本文引用地址:http://www.j9360.com/article/157768.htm

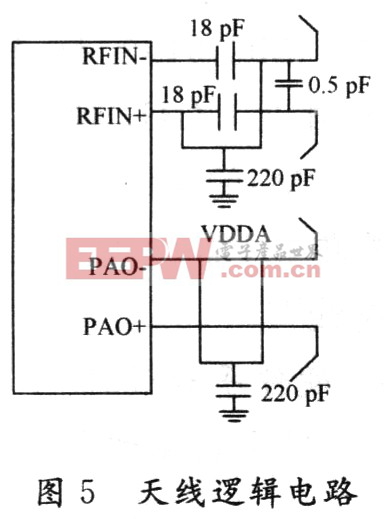

(2)天線電路的設計。用于2.4 GHz射頻電路的天線有3種類型:外接直立天線、PCB天線和片式天線。外接直立天線的性能最好,但體積過大,只能用于對體積無要求的場合;片式天線采用集成電路來實現,性能一般,而且很難根據實際調整性能;PCB天線具有體積優勢,但是對設計和PCB布線要求高,在無線傳感器網絡的硬件平臺上應用最多。

圖5為天線電路的原理圖。RFIN-和RFIN+為接收通道,2個18 pF的電容過濾掉高頻干擾信號,而0.5 pF的電容能防止共扼干擾。PAO-和PAO+為發送通道,這兩個管腳和VDDA連在一起,給發送通道提供必要的能量。

3 MIT-ZigBee硬件平臺的模塊測試

在完成硬件電路設計后,必須對各模塊的硬件電路進行測試,以保證硬件電路的可靠性。對于整塊的硬件電路,應該按模塊分別焊接、調試,并逐模塊調試通過后再聯合起來一起調試。在硬件PCB設計時需要預留出一定的測試節點,以便以后測量使用。

MT-ZigBee主要模塊的基本測試流程如下:

(1)電源模塊測試。在空的PCB電路板上首先將電源模塊的相關元器件焊接好,上電后直接利用萬用表測量電源的輸出點,看是否得到要求的電壓值,以保證其他模塊能正常工作。

(2)微控制器部分測試。當電源模塊工作正常后,就需要測試GB60是否正常工作。對于MCU的測試主要就是通過BDM燒寫器與GB60通信,看是否能進行正常的擦除與寫入操作。若無法正常工作,則首先就應該仔細核對MCU支撐電路及電阻、電容的值是否正確,特別是晶振電路部分。GB60含有4 MHz的內部時鐘源,且外圍電路很少,所以比較容易調試通過。

(3)MC13192模塊測試。對于MC13192射頻模塊的測試,主要是通過讀寫其內部的寄存器和緩沖區來進行測試的。

(4)其他外圍模塊測試。串行通信(SCI)是通過PC實現基本的收發;測試小燈模塊,主要通過MCU將相應的I/O口置不同的值,看是否能點亮對應的小燈;測試液晶LCD模塊,看是否在液晶上顯示指定的字符。

4 結 語

這里主要為ZigBee協議棧的實現提供了相應的硬件平臺設計。在MT-ZigBee平臺硬件芯片選型的基礎上,給出硬件平臺的整體框架,闡述了硬件平臺電源電路、GB60與MC13192接口電路和MC13192射頻模塊的詳細設計。最后,還對MT-ZigBee硬件平臺進行了各個模塊的測試。由于篇幅有限,實現ZigBee技術相關的底層協議棧設計和具體驗證協議棧可用性的應用實例在此中沒有介紹。

評論