基于FPGA視頻采集中的I2C總線設計與實現

4 設計仿真結果

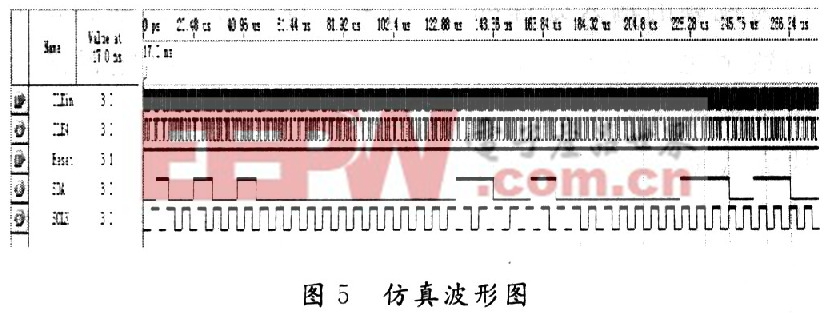

設計中利用QuartusⅡ集成環境采用VHDL語言實現了I2C總線對SAA7111中集成的symbol進行實驗仿真。reset信號為外接復位信號,時鐘信號根據需要外接所需頻率時鐘信號(clk),并根據要求對信號進行16分頻作為進程激勵信號(clkin)。對于上述初始化數據,仿真波形如圖5所示仿真結果輸出正確后,配置與電路設計相符的入/輸出引腳。根據測試結果,該設計可以穩定可靠地對SAA7111進行參量控制,如果需要修改只需更換程序中參量,再次編譯下載即可。

5 結語

該設計在視頻采集處理系統中已得到應用,I2C總線接口數據采集正確、穩定,并且在實現過程中,占用資源少,僅為總資源的40 %。核心器件與圖像數據采集芯片配合使用,節省核心處理芯片的通用I/O接口,使系統整體電路十分簡潔、可靠性高、集成度高、接口方便等優點。

評論