Modbus通信協議的FPGA實現

3.3 發送模塊

發送模塊包括發送控制模塊,發送機模塊,發送狀態寄存器模塊等。

發送機模塊是基于普通UART發送原理設計,其發送過程如下:

(1)等待TDRE=‘1’,即等待發送數據寄存器(TDR)為空,隨后TDR中載入一個字節數據,并把TDRE清零。

(2)根據波特率設置Sel_baud[1..0]對TDR里的數據進行奇偶校驗計算。

(3)把TDR里的數據放入發送移位寄存器TSR的1~8位,TSR第O位放起始位(‘O’),TSR第9位放入奇偶校驗位或者停止位(‘1’)。

(4)通過對TSR右移,一位一位地發送出9位數據比特,最后發送停止位(‘1’)。

3.4 CRC模塊

CRC模塊包括接收CRC控制模塊,發送CRC控制模塊,CRC產生模塊三部分。

生成CRC的過程為:

(1)將一個16位寄存器裝入十六進制FFFF(全1),將之稱作CRC寄存器。

(2)將報文的第一個8位字節與16位CRC寄存器的低字節異或,結果置于CRC寄存器。

(3)將CRC寄存器右移1位(向LSB方向),MSB充零,提取并檢測LSB。

(4)如果LSB為0:重復步驟(3)(另一次移位);如果LSB為1:對CRC寄存器異或多項式值0xA00l(1010000000000001)。

(5)重復步驟(3)和(4),直到完成8次移位。當做完此操作后,將完成對8位字節的完整操作。

(6)對報文中的下一個字節重復步驟(2)~(5),繼續此操作直至所有報文被處理完畢。

(7)CRC寄存器中的最終內容為CRC值。

這種方式計算CRC值的時間比其他方式計算CRC(比如查表法等)的時間稍微要長,但是它節省了資源,比如查表法計算CRC需要一個數組來存放所有可能的CRC結果值。圖5為對數據串“010300000001”(十六進制)CRC-16運算的仿真時序圖,時鐘周期為50 MHz,由圖可見,整個計算時間在2.5 μs內,估算一個含有240個字符的消息,CRC校驗總時間約為2.5μs×(240/6)=100μs,這樣長的校驗計算時間對于Modbus協議來說是完全可以接受的。

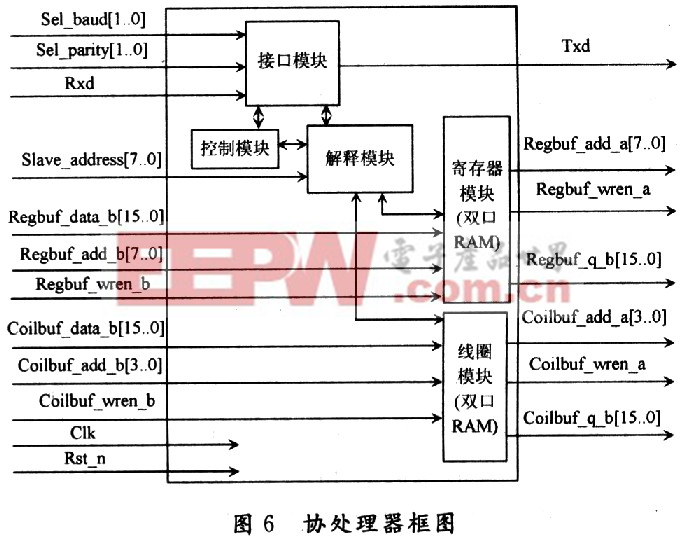

4 基于該接口的MODBUS從站協處理器實現

協處理器框圖如圖6所示。

從站協處理器控制模塊程序控制過程如下:

(1)置CE_Modbus為‘1’,把MAX485芯片![]() 信號輸出置低,即控制RS 485接口芯片處于接收狀態。

信號輸出置低,即控制RS 485接口芯片處于接收狀態。

(2)等待一段延遲時間(RS 485接口芯片穩定時間),使能Modbus協議接口模塊即置CE_Modbus為‘1’,并置接收Modbus協議幀模式。

(3)如果接收到一個完整的幀(消息),則轉到步驟(4),如果沒接收到一個完整的消息,一直處于等待狀態。

(4)先置CE_Modbus為‘O’,再解釋接收緩沖寄存器里消息,等待消息處理完畢,如果消息不是發往該從站或者為廣播消息,則轉到步驟(2);否則把![]() 信號輸出置高,轉到步驟(5)。

信號輸出置高,轉到步驟(5)。

(5)等待一段延遲時間,使能Modbus協議接口模塊即置CE_Modbus為‘1’,并置發送Modbus協議幀模式。

評論