FPGA與GPS-OEM板的串行通訊系統設計

3.2數據校驗和存儲設計

要正確讀取OEM板的輸出語句,首先是判斷語句類型,其次是存放數據,然后再確定語句的結束標志。本例中將接收的數據存放在FPGA內部設定的RAM中,而對時間,位置等信息的提取和處理則在其它部分完成。

數據校驗模塊由FIFO的滿信號啟動。當檢測到滿信號有效時。校驗模塊連續的讀取數據并進行處理。當檢測到起始標志$后,即進入數據讀取和檢測。輸出數據是以語句的形式出現的,每條語句代表一種數據,每種數據都有它自己的識別碼,所以,要根據收到的語句識別碼來判斷該語句是否為所需要的內容(如GPRMC中,GP為識別符,RMC為語句名)。

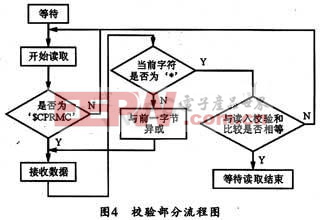

根據NMEA-0183通信標準格式的內容,可對所接收到的數據進行檢驗。即對接收到的信息逐字節異或。當接收到*時,比較下一字符hh與實際異或值是否相等。若相等,即所接收的數據正確;若不等,則所接收數據無效,系統隨之復位存儲設備,并等待檢測下一組數據。當檢測到結束符CR>LF>時,標志數據讀取結束,系統向FIFO發出結束標志,并等待下一次數據檢測。其系統校驗流程圖如圖4所示。

4 結束語

本文結合PFGA和GPS-25型OEM板的硬件特點,分析了FPGA和OEM板的串行通訊問題,同時重點分析了讀取GPS定位信息的設計問題。

評論