航管二次雷達射頻切換單元FPGA實現

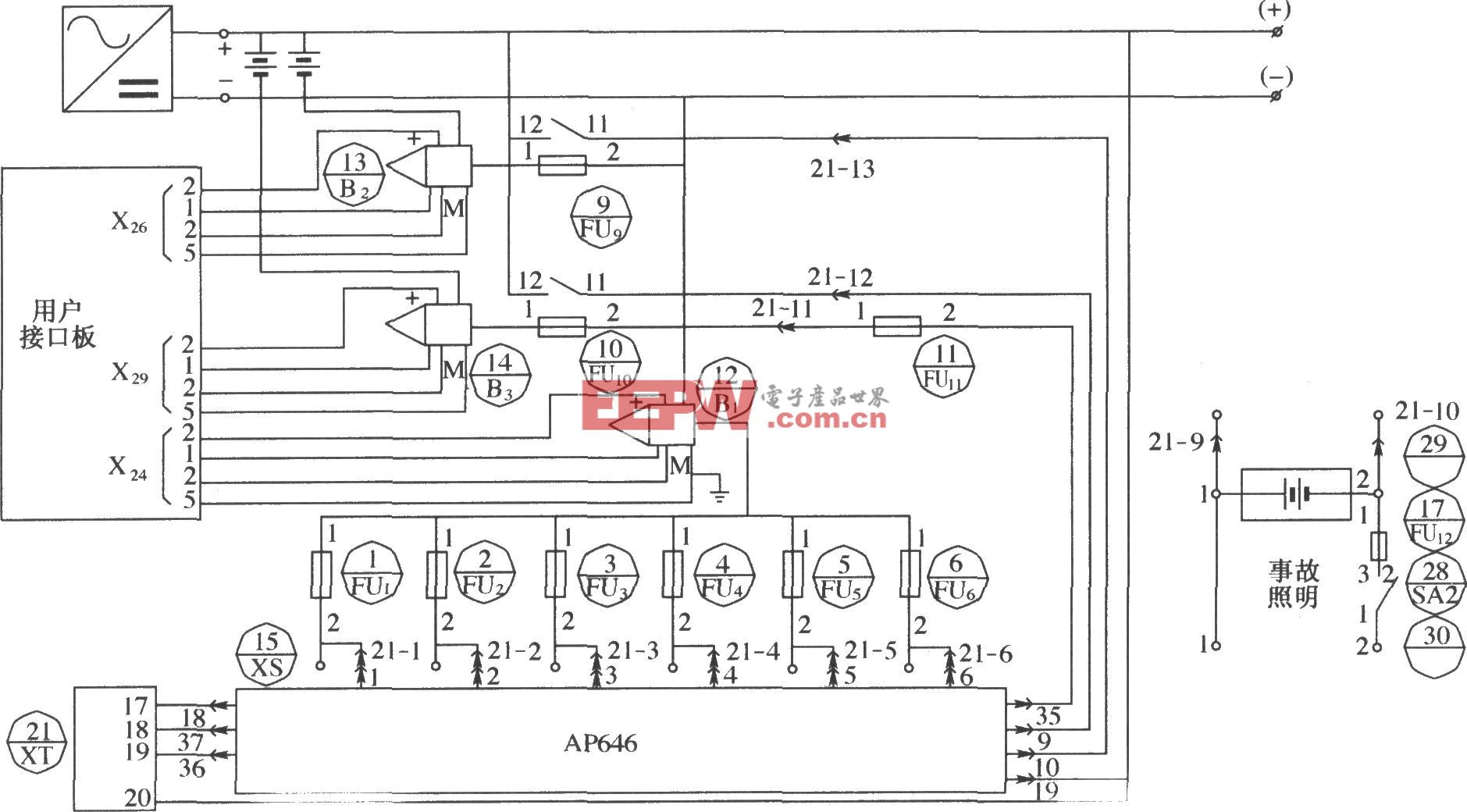

在射頻切換系統的控制電路中,選用Lattice公司的EPLD作為主處理芯片(ispLS11032E),該芯片有64個I/O端,8個指定輸入端,6 000個邏輯門,192個寄存器,最大時延小于等于12 ns,通過簡單的5線接口,即可用PC機對線路板上菊花鏈結構的最多8個芯片進行編程。

切換開關工作原理為:A通道輸入選通控制脈沖時,如當前開關工作在A通道,則維持在A通道,不作切換;如當前開關工作在B通道,則切換到A通道。同樣,B通道輸入選通控制脈沖時,如當前開關工作在B通道,則維持在B通道,不作切換;如當前開關工作在A通道,則切換到B通道。即同時工作在A通道或同時工作在B通道,三路開關的狀態隨時通過控制電纜以TTL差分方式送給數據處理。

在射頻切換控制板中信號流程如下:監控計算機發出的差分切換脈沖經差分接收器接收后,進入可編程EPLD,在EPLD內利用硬件語言實現了對切換脈沖的濾波、脈沖判斷、框架判斷等,確認該信號為計算機切換命令而不是外來干擾后,發出切換信號到驅動單元,切換信號經驅動單元到開關TN6K31的控制端,實現切換動作。

2 系統實現的具體細節

2.1 信號濾波與毛刺抑制

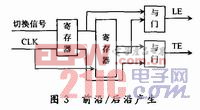

二次雷達監控計算機發出的通道切換信號是脈沖編碼信號。由于雷達工作電磁環境復雜,所以在系統內部要判斷該信號是否為于擾信號,在系統中首先進行切換信號前、后沿的提取,將切換信號輸入兩個寄存器,加以門電路實現,如圖3所示。

LE與TE分別切換信號的前沿與后沿,在經過一系列寄存器,使前沿與后沿分別用觸發器進行延時,根據前沿與后沿間間隔可以判斷出脈沖的寬度,對于不符合切換條件的毛刺與噪聲進行抑制。

2.2 框架檢測

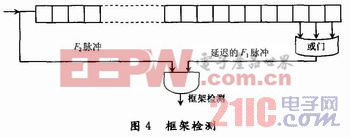

正常情況下,監控計算機發出的切換脈沖的兩個脈沖的間隔為20 ms,在切換控制系統中使用的時鐘為8.276 MHz,因此,一個切換命令的兩個脈沖的時間間隔就認為兩個前沿間有167,168或169個時鐘周期。在該系統中,脈沖編碼的檢測是根據比較延時的前沿與非延時情況下的重合情況,延時的前沿對應于框架脈沖F1,非延時的前沿對應脈沖F2,F1相對于F2延時20ms,由于F2相對于F1有三個時鐘脈沖的變化范圍,F2與F1的前沿延時167,168或169個時鐘周期的任一個對齊,都認為是一個正確的框架。框架檢測示意如圖4所示。

3 結語

雷達的發展和更新換代不僅對雷達的性能提出了更高的要求,而且對實現的方式也提出了新的要求。集成度高、性能好、體積小已經成為雷達設計的必然要求。飛機密度的不斷增加,對雷達系統的可靠性,提出了更嚴格的要求,為了提高可靠性,現代雷達使用雙機熱備份冗余設計,雙機中切換部分的可靠性關系到雷達的整體性能,用硬件設計語言編程EPLD方法處理二次雷達的切換信號具有很大的優越性。

評論