TMS320F28335與串行A/D轉換器ADS7863的接口設計

3 TMS320F28335 McBSP與ADS7863接口設計

3.1 硬件接口設計

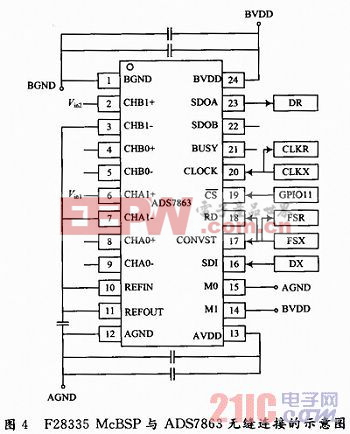

圖4是TMS320F28335 McBSP與ADS7863無縫連接的示意圖。從圖中可以看出,McBSP與ADS7863之間的連接非常簡單,實現了數據的高效轉移,充分體現了同步串口連接的優點。由F28335 DSP的GPIO11向ADS7863提供片選信號。McBSP的數據發送DX腳接ADS7863的SDI腳,向ADS7863發出控制信號。ADS7863的SDOA腳接McBSP的數據接收DR腳,向F28335傳送數據信號。由MeBSP內含的可編程采樣率發生器生成時鐘信號CLKG和幀同步信號FSG。由CLKG驅動發送時鐘信號CLKX,CLKX驅動接收時鐘信號CLKR和ADS7863的時鐘信號CLOCK。由FSG驅動發送幀同步信號FSX,FSX驅動接收幀同步信號FSR和ADS7863的開始轉換信號CONVST。CONVST初始化一個轉換進程,并啟動發送前一周期轉換的數據。為了簡化,只連接了ADS7863的CHA1+和CHB1+通道,可用輸出數據的第二位(ADC指示符)分辨所采樣的信號來自哪個通道。本文引用地址:http://www.j9360.com/article/155952.htm

3.2 軟件接口設計

3.2.1 McBSP口初始化

整個初始化過程包括三部分:接收部分初始化、發送部分初始化和采樣率發生器初始化。

(1)DSP初始化后,采樣率發生器的初始化位GRST=0;在其他情況下,也可通過向SPCR2寄存器中的GRST位置0,使采樣率發生器處于初始化狀態。在此狀態下,時鐘CLKG時鐘為CPU時鐘的1/2,幀同步信號FSG為邏輯0;設置接收初始化位RRST、發送初始化位XRST和幀同步發生器初始化位FRST為0;

(2)對采樣率發生器SRGR[1,2]進行設置,并對其他控制寄存器進行設置;

(3)等待兩個CPU時鐘以確保內部正確同步;

(4)將采樣率發生器初始化位置1,使采樣率發生器進行工作;

(5)等待兩個SRG時鐘;

(6)將接收和發送初始化位置1;

(7)在下一個CPU時鐘的上升沿,CLKG時鐘發送一個1,并以CPU時鐘/(1+CLKGDV)的頻率運行;

(8)在數據發送寄存器DXR[1,2]被載入數據后,將幀同步初始化位置1以發出正確的幀同步脈沖信號。

下面是McBSP初始化程序片段:

評論