超高速雷達數字信號處理技術簡介

本文引用地址:http://www.j9360.com/article/153757.htm

五、超高速數據采集系統的實現

對于1m距離分辨率的雷達系統,其采樣速率可以達到250MS/s,其主要問題是:

1.體系結構的選擇

(1)AD變換的體系結構[17] 在AD轉換模塊中,可以采用單片AD的結構,也可以采用多片AD并行的結構;而多片AD并行又包括時間并行和幅度并行兩種方式.多片AD并行可以降低對每一AD芯片的性能要求,但增加了設備量和控制的復雜性.在超高速應用的場合,一般采用的是單片AD變換的結構.

(2)數據存儲的體系結構[18] 由于超高速數據采集系統的速度很快,因此存儲模塊的設計一般都采用分路數據輸出的體系結構;這種結構將AD的輸出數據分成多路較低速數據輸出,可以降低對存儲器讀寫速度的要求.

2.元器件的選型與信號連線的處理

根據表1,對于250MS/s的數據采集系統,傳統的TTL芯片已無法工作.目前常用的超高速標準芯片系列是ECL芯片;對于250MS/s的采樣速率,ECL10KH系列可以滿足要求.

根據前面的分析,超高速系統的信號連線必須采用微波傳輸線作為信號之間的連線,并要進行正確的端接.這樣就可以消除反射,并精確控制信號的延遲.

3.模擬電路的抗干擾

系統抗干擾的方法首先是屏蔽,包括電路整體的屏蔽以及系統模擬部分和數字部分之間的屏蔽.但是由于超高速系統一般是高功耗的,因此還必須兼顧散熱問題.

數據采集系統中數字電路對模擬電路的干擾是主要誤差源之一.消除這一干擾可以通過器件的隔離、電源濾波、星形接地以及元器件的合理布置來解決.在超高速系統的實現中,大面積地是一個最基本、也最重要的因素之一,一方面它可以減小干擾,另一方面它也是微帶傳輸線的一個組成部分.

4.系統的實現與性能測試

(1)系統的實現 系統中采用了單片超高速AD芯片加全局存儲器的體系結構,并采用單片機構成系統與IBM-PC計算機的接口,使數據采集的結果可以在計算機中顯示并加以處理(圖1).其中,為降低對存儲器速度的要求,采用了分路數據輸出的方式,使存儲器的速度降低為AD變換速度的一半.存儲器的周邊器件采用ECL芯片.信號之間的連線采用微帶或帶狀傳輸線,并端接了合適的端接電阻.

圖1 超高速數據采集系統的體系結構

(2)系統性能測試 數據采集系統的性能測試主要包括靜態測試和動態測試,其中動態測試更能夠全面地反應系統的性能.在動態測試中最為關心的指標是動態有效位(ENOB).本系統在250MS/s采樣速率、125MHz輸入信號時測試了系統的動態有效位,可以證明,系統的動態有效位在7-bit以上.

六、高速數字脈沖壓縮系統的實現

1.脈沖壓縮的基本原理[8]

脈沖壓縮算法的基礎在于匹配濾波的理論.假設發射信號為S(t),其頻譜為S(ω);并設匹配濾波器的沖擊響應為h(t),傳遞函數為H(ω),則脈沖壓縮后的信號輸出為:

Y(ω)=H(ω).S(ω) (1)

y(t)=h(t)

s(t) (2)

這里,只要匹配濾波器的沖擊響應/傳遞函數與發射信號滿足匹配濾波關系,就可以獲得脈沖壓縮的輸出結果.

2.脈沖壓縮的主要實現方法

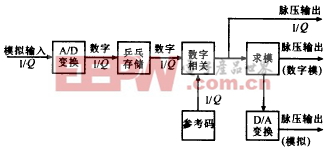

(1)時域法實現脈沖壓縮 時域法實現脈沖壓縮的基礎是式(2):由于匹配濾波在時域等效于相關接收,因此,時域法實質上就是數字相關的方法.圖2顯示了相關數字脈壓的基本結構.其中,采集的原始信號與預先存儲的參考碼送入相關器,相關器的輸出就是脈壓后的數字結果;可以采用DA變換將其變為模擬信號顯示.

圖2 時域法實現數字脈壓

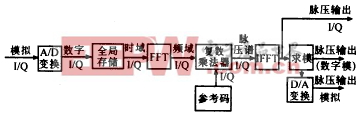

(2)頻域法實現數字脈壓 頻域法實現數字脈壓的基礎是式(1),其基本結構示于圖3.這里,采集的原始信號首先通過FFT變換到頻域,與預先存儲的參考碼相乘后,再通過逆FFT變換回時域,就構成脈壓后的數字結果;同樣可以采用DA變換將其變為模擬信號顯示.由于FFT算法相當于快速卷積,因此頻域法的運算速度一般要快于時域法,尤其在壓縮比較大的情況下.

圖3 頻域法實現數字脈壓

合成孔徑雷達相關文章:合成孔徑雷達原理

評論