TMS320C542在脫機視頻編/解碼系統中的應用

2.4 圖象數據存儲SRAM

為了實現數據傳輸的流速控制,需要存儲器緩沖數據。同時,要實現圖象凍結和其它一些處理功能,也同樣需要足夠的存儲空間。本系統選擇了128K×16bit的高速SRAM來擴展C542有限的存儲空間。C542的內部RAM占據了地址從0000~27FFh的數據區,8000~0FFFFh的的數據區已經分配給了EPROM放置程序代碼,最后只有2800~7FFFh的地址可以給SRAM使用。有一種擴展SRAM訪問地址線的方案是采用兩次尋址方法。第一次先給出部分地址并緩存下來,此時不訪問數據;在第二次訪問時,給出余下的地址數據,然后利用拼接的總地址來訪問數據。

由于圖象數據是數據流,它在SRAM中的存放和讀取都是地址順序遞增的。依據這一特點,本系統設計了一種新的SRAM地址線擴展方法。該方法將每32個16位字圖象數據劃分為一次數據操作的最小單元組。這32個字數據在SRAM中存放地址的高12位是一樣的,這高12位地址用DSP的低12位地址線選擇。而SRAM的低5位地址用一個5位二進制計數器自動遞增生成,即每訪問一次高12位地址,低位地址自動增1.這樣,實際只用了DSP的12根地址線,就可以高效地訪問SRAM的所有存儲空間。最后,DSP地址線的高四位A15~12應該在0011~0111之間選擇兩個值,一個用來片選SRAM,一個用來復位計數器。

2.5 數據通信高速串口

本系統直接利用C542的緩沖串口BSP作為系統開放給用戶的通信接口。該接口的數據速率最高可以達到40Mbps,數據包的長度可以在8位、10位、12位和16位之中選擇。BSP串口的接收部分BSPR操作在被動方式下,伴隨接收數據的時鐘和幀同步信號應該由外部提供。BSP串口的發送部分BSPX既可以工作在主動模式下,其數據時鐘和幀同步由DSP內部提供。BSPX也可以工作在被動模式,數據時鐘和幀同步時鐘由外部輸入。BSP的緩沖區數據自動發送和接收功能,也簡化了DSP的處理工作。本系統在DSP的BSP串口基礎上增加了接口驅動,構成了系統的通信接口。

3 DSP部分的系統設計

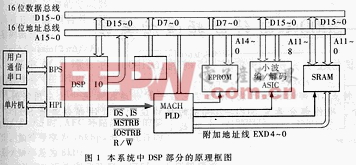

圖1是本脫機視頻編/解碼系統的核心DSP部分的構成原理圖,其中DSP的緩沖串口DSP單獨構成了用戶通信串口,DSP的HPI接口實現了DSP和低速控制單片機之間的通信。剩下與DSP的IO接口相連接的外圍是上電復位SRC數據邏輯、程序加載EPROM、視頻圖象編/解碼ASIC和圖象數據存儲SRAM。EPROM和SRAM作為DSP擴展的數據存儲區來處理,SRC數據邏輯和視頻編/解碼ASIC作為DSP的IO端口來訪問。從程序指令角度講,數據存儲區的訪問操作應該使用DSP的數據訪問指令,例如LD、ST、MVDD等等,而IO端口的訪問要使用DSP的IO端口訪問指令PORTR和PORTW。

DSP的IO接口的16位數據線和16位地址線構成外圍器件的數據總線和地址總線。小規模的MACH可編程邏輯器件被用于設計IO外圍器件的訪問控制邏輯。MACH產生的每個器件的片選和讀寫信號由它與DSP的關系、它的尋址范圍以及管腳信號特性決定。例如程序下載EPROM是DSP擴展的數據區,尋址范圍8000~0FFFFh,如果它的片選信號是高電平有效,EPROM片選邏輯為:

CS-EPROM=(!DS)A15

當DSP訪問數據區時,DS有效,為低電平,并且當地址線的最高位A15為1時,CS_EPROM信號有效,EPROM被選通。此外,用于SRAM訪問地址自動遞增的二進制五位計數器也由MACH可編程邏輯器件實現,構造出了附加的5條地址線。

通過利用DSP芯片TMS320C542所具有的DSP和HPI接口功能,并結合MACH可編程邏輯芯片擴展DSP的IO接口功能,從而實現了脫機視頻芯片擴展DSP的IO接口功能,從而實現了脫機邏輯芯片擴展DSP的IO接口功能,從而實現了脫機視頻圖象編/解碼系統的控制核心的設計。通過實際的調試,DSP能夠在上電復位時正確地從EPROM下載程序代碼并運行,DSP可以正確地訪問視頻編/解碼ASIC和數據存儲SRAM,DSP與單片機的命令數據交換和串口數據的傳輸都能正常實現。這個結構合理、布局緊湊的硬件設計為進一步的軟件開發提供了方便。DSP對外圍數據訪問的指令代碼,特別是對SRAM的訪問操作,簡單高效,這為DSP程序軟件中其它圖象實時控制算法節省了寶貴的指令周期資源。

評論