FPGA和單片機的串行通信接口設計

if oddb='1' then

sout1='0';state=stop2;

else

sout1='1';state=stop2;

end if;

when stop2=>

sout1='1'; --停止位

if len=0000000000000000 then

state=stop2;

else

state=start1;

len=len-1;

end if;

end case;

end if;

end process;

sout=sout1;

end behav;

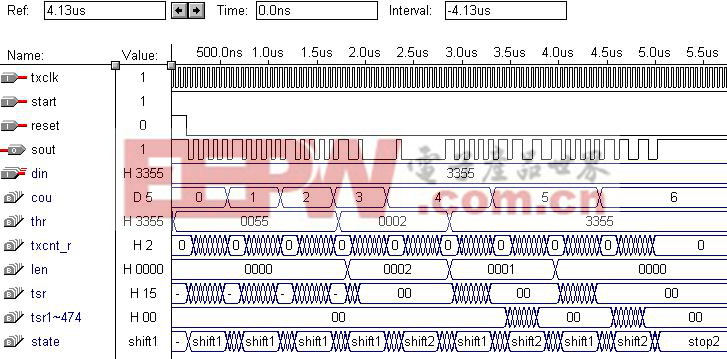

其中各信號的說明已在程序中標明了。波形仿真圖如圖2所示。

圖2 FPGA數據發送時序仿真圖

圖中Din寫入值為3355H,波特率為2400Hz,Start信號始終置邏輯1,即隨時都能發送數據。Reset信號邏輯1時復位,邏輯0時電路開始工作。THR是數據寄存器,文件頭、數據長度以及數據位都先寄存到THR中,Len是數據長度,TSR是低8位數據幀寄存器,TSR1是高8位數據幀寄存器。數據長度Len定為02H,發送時先發送低8位55H,后發送高8位33H,一共發送兩遍。發送的數據格式說明:當發送55H時,其二進制為01010101,則發送的數據的二進制數為00101010111(1位開始位+8位數據位+1位奇校驗位+1位停止位)。

單片機部分先對FPGA發送過來的文件頭進行確認,正確就接收文件,否則放棄接收的數據。根據FPGA發送模塊的協議,對串口控制寄存器SCON和波特率控制寄存器PCON的設置即可實現。本文引用地址:http://www.j9360.com/article/151789.htm

3 總結

目前電子產品的開發中經常要綜合運用EDA技術、計算機控制技術、數字信號處理技術,那么電路各部分經常需要數據交換。本文也是基于此給出這方面應用的實例,供開發者交流。

評論