基于上位機與FPGA開發板的光纖通道接口適配器

2.3 Virtex-5開發板的底層保證

(1)系統構造邏輯設計主要完成以下幾點功能:

控制PCIE硬核實現與上層軟件交互;對上層傳輸數據加CRC校驗;完成FC鏈路初始化過程;完成FC流控功能;完成FC-2差錯處理;控制ROCKET I/O把上層軟件數據通過ROCKET I/O發送;控制ROCKET、I/O把接收恢復的數據傳輸到上層軟件。

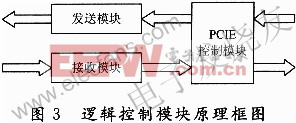

(2)邏輯設計的模塊組成:底層邏輯控制模塊主要完成FC物理層通信,它主要包括發送模塊、接收模塊和PCIE控制模塊三部分,每個模塊又根據功能不同劃分多個子模塊,在PCIE控制模塊中,有一些緩存來存放接收模塊傳送過的數據和相應的數據信息,發送模塊也會從PCIE控制模塊的緩存中讀取數據傳送出去,其原理框圖如圖3所示。

數據發送模塊 該模塊通過讀取上位機的狀態信息來發送不同的信息,當ACK使能時,該模塊發ACK,當數據使能時,該模塊就發送固定幀數的數據,發送的數據是從緩存中讀取,CRC由該模塊添加。空閑時就發送IDLE碼。

數據接收模塊 接收模塊包括接收控制模塊、CRC模塊和臨時緩存模塊。主要完成數據和鏈路控制幀以及準備信號的接收,并實現CRC校驗,根據幀頭來判斷不同類型的數據幀或控制幀,并存入緩存中,同時將幀的相關信息也放入相應的緩存中。

PCIE接口控制模塊 該模塊主要根據PCIE總線上的地址對應的寄存器的值,譯碼成相應的使能把PCIE總線上數據寫入相應的數據發送buf-f,ACK發送 buff反之根據邏輯輸入的使能,譯碼成對應的PCIE總線上對應地址的對應寄存器的值,并把數據接收的buffACK接收buff數據寫入相應的PCIE地址上。

2.4 最終實現

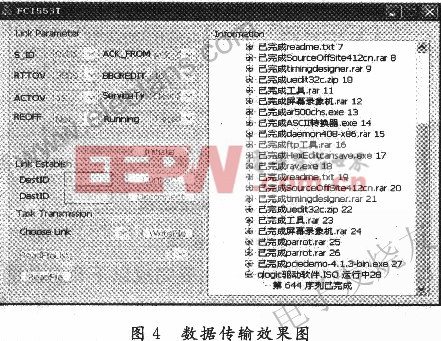

通過上位機與FPGA開發板的結合,實現了光纖通道接口適配器的高速性。傳輸效果圖如圖4所示。

3 結語

通過上位機與FPGA開發板的結合,模擬并實現了光纖通道在高速數據傳輸過程中接口處的設計。盡管該設計是上位機配合FPGA的形式實現,但僅就設計思路而言,對于實際開發光纖通道接口適配器具有一定的借鑒意義。

評論