基于中檔FPGA多相濾波器的設計實現

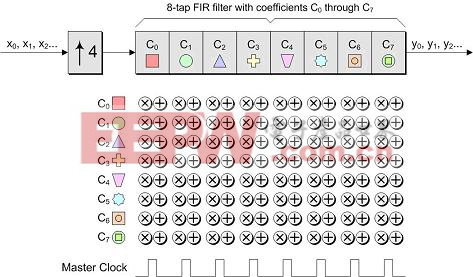

除了任何寄存器和一般用途的邏輯,常規8抽頭FIR濾波器中的每個抽頭包含一個乘法器和一個加法器,當然為我們提供了總共8個乘法器和8個加法器。濾波器之后需要一些額外的邏輯,以便丟棄任何不想要的樣本。

同樣,在我們最初的4 × 2抽頭多相實現中的每一個抽頭含有一個乘法器和一個加法器,再次為我們提供了總共8個乘法器和8個加法器。在多相實現中,需要實現“旋轉開關”送入濾波器的邏輯數量大約相當于在常規8抽頭FIR濾波器中丟棄不要的樣本所需的邏輯。

當然,多相實現還需要一些額外的邏輯和一個加法器累加來自四個子濾波器的結果。因此,最終的結果是,最初的多相實現需要比傳統的8抽頭FIR濾波器更多一點的邏輯。

然而,對于傳統的8位FIR濾波器,在每個時鐘都要執行8次乘和8次加。相比最初的多相實現的情況,在任何主時鐘時刻,只有一個子濾波器是工作的。由于在這個例子中每個子濾波器含有兩個抽頭,這意味著這個功能的濾波器部分在每個時鐘只進行兩次乘法和兩次加法。

當然,從四個子濾波器收集結果的求和功能還必須在每個主時鐘進行加(在每4時鐘周期開始時,這個累加器清零;它從四個子濾波器收集結果; 在每4時鐘周期結束時,它產生一個新的值)。

這意味著,最初的多相實現的每個子濾波器有效地以常規8抽頭FIR濾波器1/ 4的頻率運行。反過來,這意味著最初多相實現只在每個主時鐘進行兩次乘法和三次加法(包括加法器的加操作),從而大大節省了功耗。

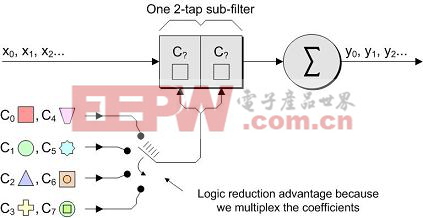

此外,在最初的多相實現中,由于四個子濾波器的每個只用了1/4的時間,這意味著在任何特定時間,我們實際上只需要其中的一個,這使我們更加完善了實現方法,如圖14所示。

圖14 更完善的基于多相濾波器的抽取器實現方案

在這種情況下,我們采用了單一的2抽頭子濾波器,每個抽頭含有乘法器和加法器。在每個主時鐘,我們選擇合適的系數對。每一個抽頭需要額外的寄存器和用于維護的邏輯,但與減少的乘法器和加法器相比,與我們的最初多相實現相比,這是微不足道的。

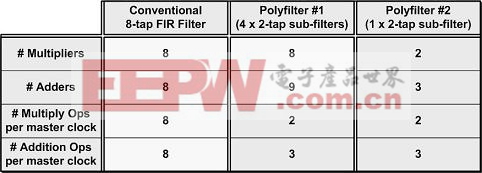

當然,在我們原來的多相實現中,我們仍然要在每個主時鐘時刻執行兩次乘法和三次加法,。這些抽取實現例子的總結如表1所示。

表1抽取實現實例的總結

利用多相FIR濾波器進行內插

現在讓我們來考慮內插的情況。首先讓我們先考慮一個基于常規8抽頭FIR濾波器的內插子系統的符號表示,如圖15所示。

圖15傳統的基于8抽頭FIR濾波器的內插器的符號表示

評論